Sun Microelectronics

83

7. UltraSPARC External Interfaces

7.3.2.3 Coherent Write Misses

If a coherent write misses in the E-Cache, the corresponding cache line is victim-

ized. When the victimized line is dirty, a writeback transaction is scheduled. In

any case, a read-to-own transaction is scheduled for the required write address.

When the read completes, the new data overwrites it in the cache. Section 7.11.1,

“Clean Victim Handling” and Section 7.11.2, “Dirty Victim Handling,” discuss

this process in more detail.

7.3.2.4 Coherent Read Followed by Coherent Write

When a read is made to the E-Cache, the three cycle latency (1–1–1 Mode) causes

the data bus to be busy two cycles after the address appears at the pins. For a

processor without delayed writes, writes must be held for two cycles in order to

avoid collisions between the write data and the data coming back from the read.

Also, electrical considerations force an extra dead cycle while the E-Cache data

bus driver is switched from the SRAMs to the UltraSPARC. UltraSPARC uses a

one-deep write buffer in the data SRAMs to reduce the read-to-write turn-around

penalty to two cycles. The write data is sent one cycle after the address

(Figure 7-9). There is no penalty for write-to-read transitions.

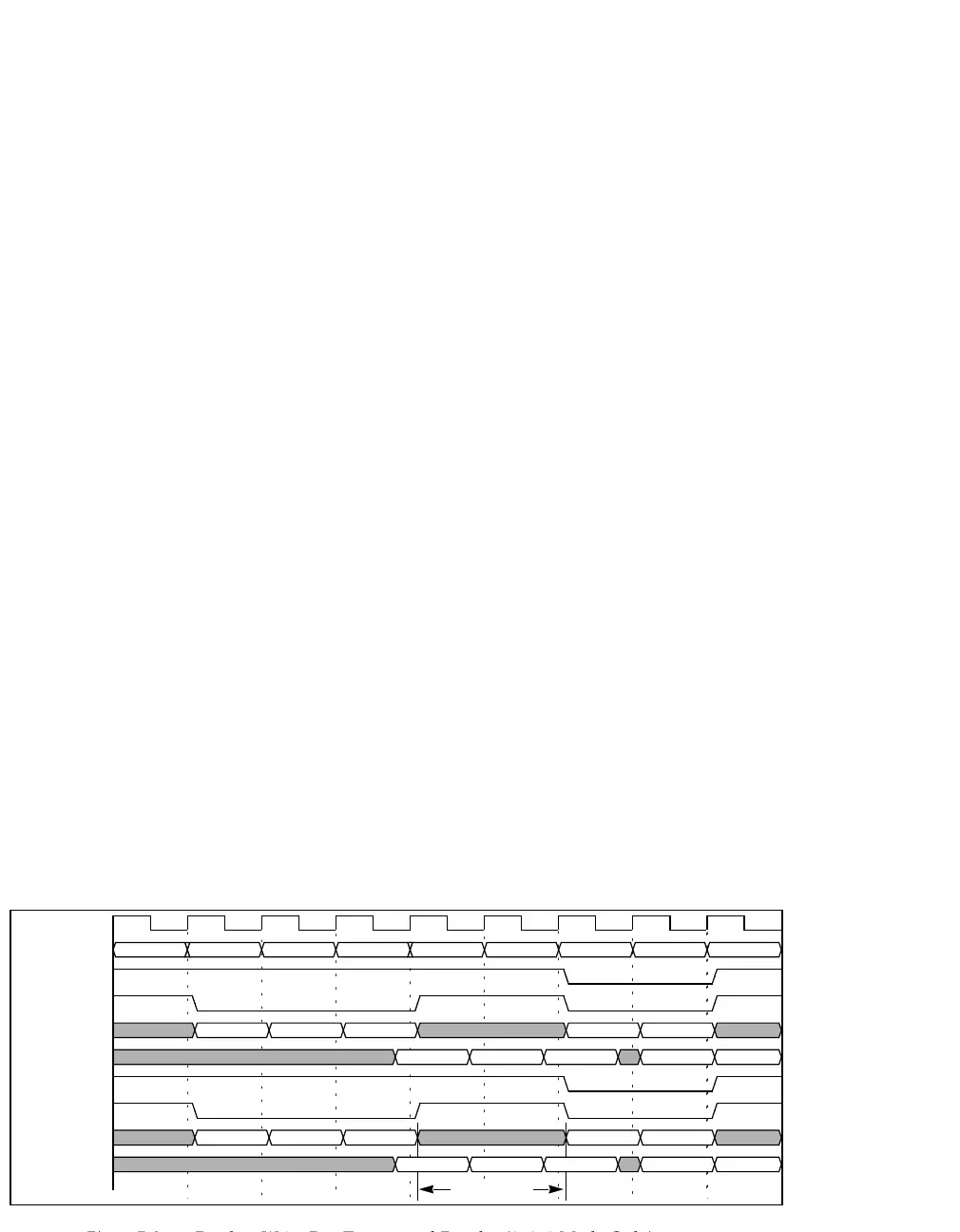

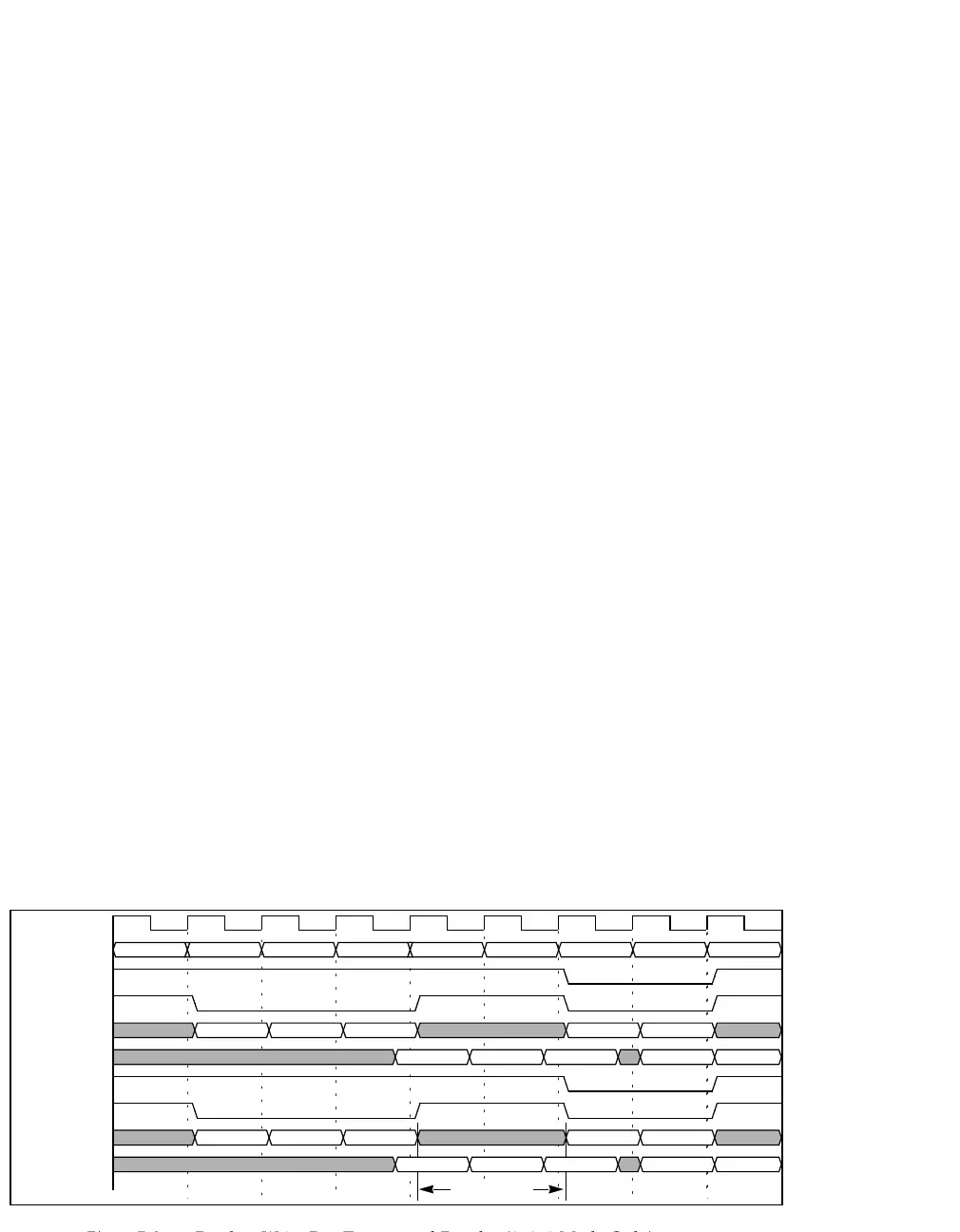

Figure 7-9 shows the two cycle read-to-write turnaround penalty for 1–1–1 Mode.

The figure shows three reads followed by two writes and two tag updates. The

two cycle penalty applies to both tag accesses and data accesses (two stalled cy-

cles between A2_tag and A3_tag as well as between A2_data and A3_data). There

is no read-to-write turnaround penalty for 2–2 Mode.

Figure 7-9 Read-to-Write Bus Turnaround Penalty (1–1–1 Mode Only)

CLK

CYCLE

012345678

TSYN_WR_L

W3 W4

TOE_L

R0 R1 R2 W3 W4

ECAT

A0_tag A1_tag A2_tag A3_tag A4_tag

TDATA

D0_tag D1_tag D2_tag D3_tag D4_tag

DSYN_WR_L

W3 W4

DOE_L

R0 R1 R2 W3 W4

ECAD

A0_data A1_data A2_data A3_data A4_data

EDATA D0_data D1_data D2_data D3_data D4_data

Staalls

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...