8–4 Chapter 8: Transaction Layer Protocol (TLP) Details

Receive Buffer Reordering

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

■ For memory read and write request with addresses below 4 GBytes, requestors

must use the 32-bit format. The Transaction Layer interprets requests using the

64-bit format for addresses below 4 GBytes as an Unsupported Request and does

not send them to the Application Layer. If Error Messaging is enabled, an error

Message TLP is sent to the Root Port. Refer to “Errors Detected by the Transaction

Layer” on page 12–3 for a comprehensive list of TLPs the Hard IP does not

forward to the Application Layer.

■ The Transaction Layer sends all memory and I/O requests, as well as completions

generated by the Application Layer and passed to the transmit interface, to the

PCI Express link.

■ The Hard IP can generate and transmit power management, interrupt, and error

signaling messages automatically under the control of dedicated signals.

Additionally, it can generate MSI requests under the control of the dedicated

signals.

■ In Root Port mode, the Application Layer can issue Type 0 or Type 1 Configuration

TLPs on the Avalon-ST TX bus.

■ The Type 1 Configuration TLPs are sent downstream on the PCI Express link

toward the Endpoint that matches the Completer ID set in the transmit packet.

If the bus number of the Type 1 Configuration TLP matches the Subordinate

Bus Number register value in the Root Port Configuration Space, the TLP is

converted to a Type 0 TLP.

■ The Type 0 Configuration TLPs are only routed to the Configuration Space of

the Hard IP and are not sent downstream on the PCI Express link.

Receive Buffer Reordering

The RX datapath implements a RX buffer reordering function that allows posted and

completion transactions to pass non-posted transactions (as allowed by PCI Express

ordering rules) when the Application Layer is unable to accept additional non-posted

transactions.

The Application Layer dynamically enables the RX buffer reordering by asserting the

rx_mask

signal. The

rx_mask

signal blocks non-posted request transactions made to

the Application Layer interface so that only posted and completion transactions are

presented to the Application Layer. Table 8–2 lists the transaction ordering rules.

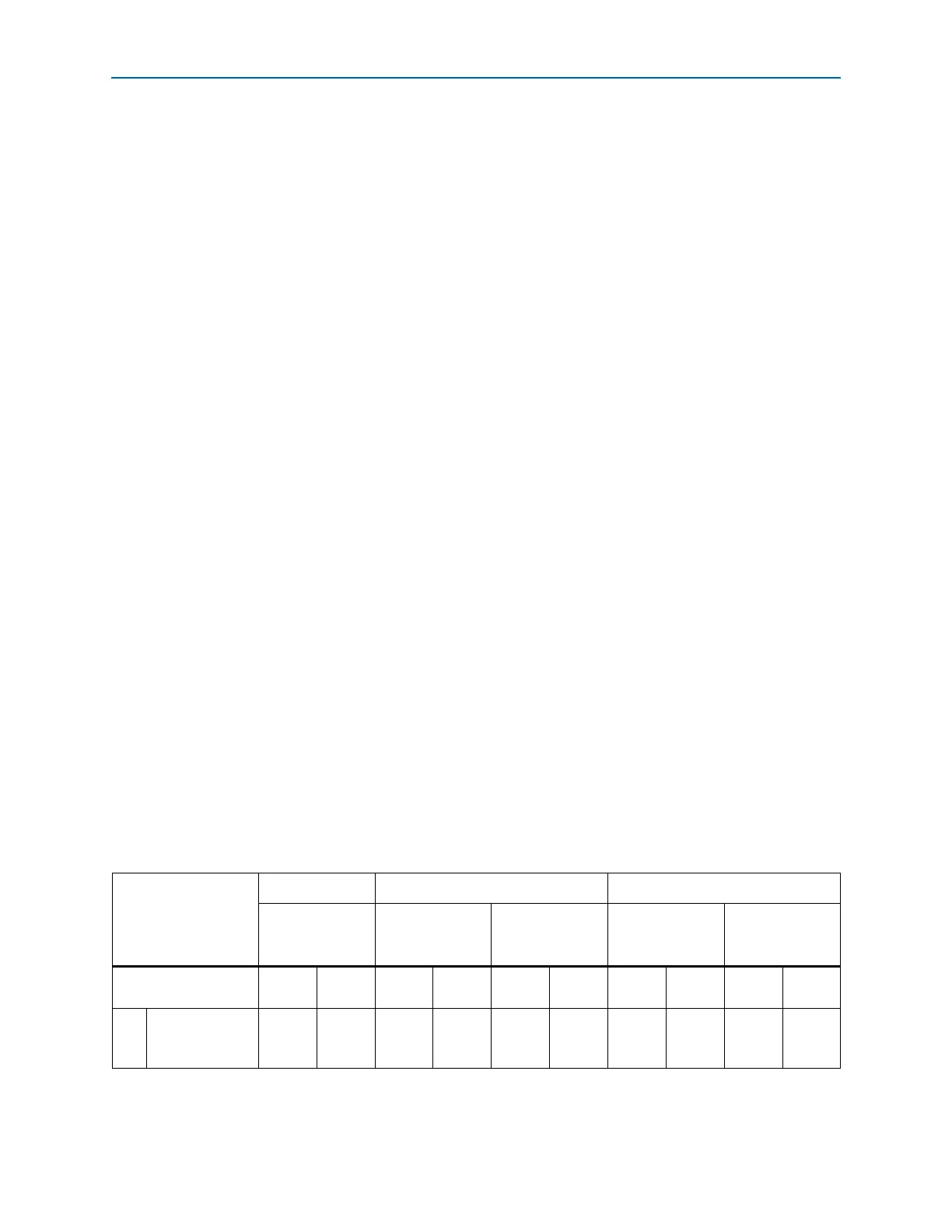

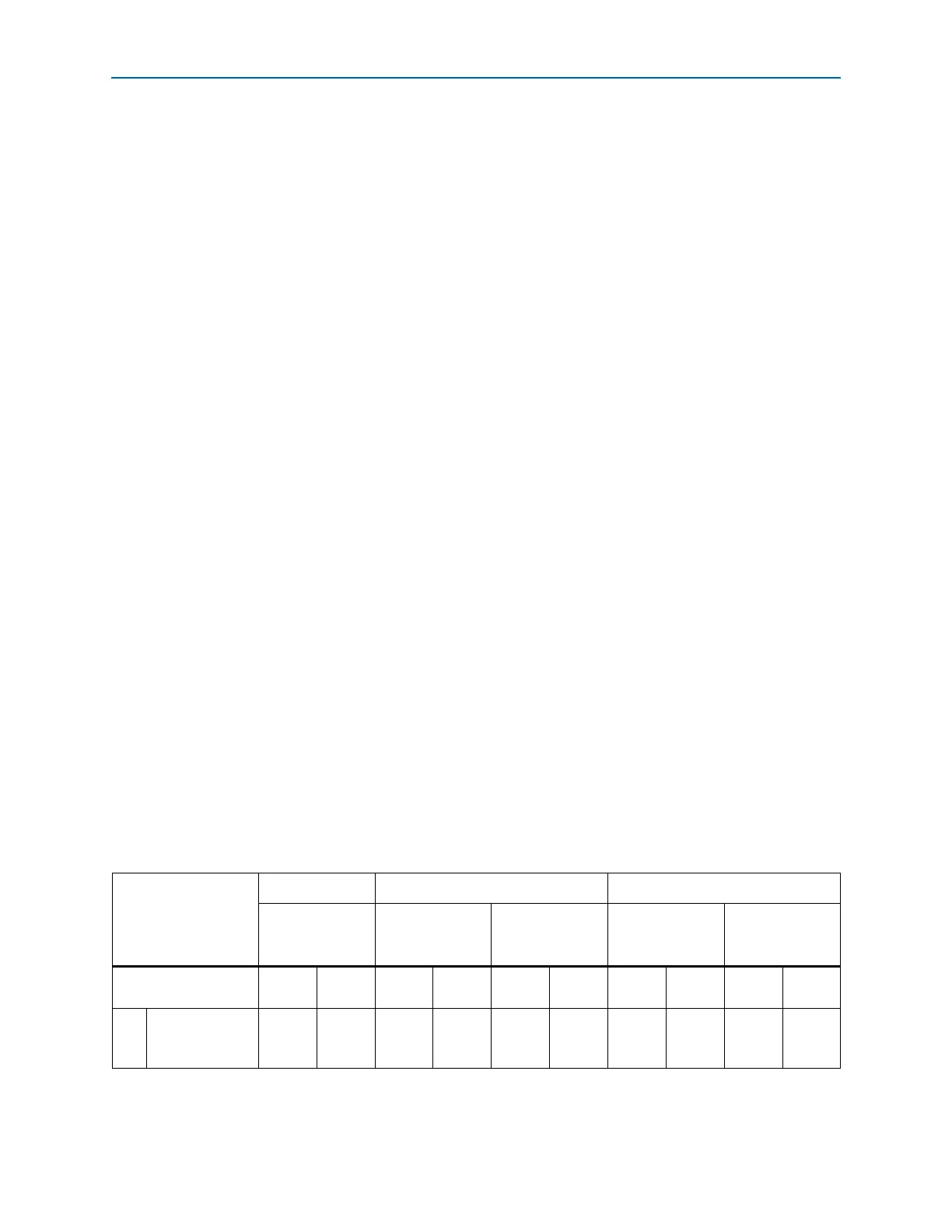

Table 8–2. Transaction Ordering Rules

(1)– (9)

(Part 1 of 2)

Row Pass Column Posted Request Non Posted Request Completion

Memory Write or

Message

Request

Read Request

I/O or Cfg Write

Request

Read Completion

I/O or Cfg Write

Completion

Spec

(10)

Hard IP Spec Hard IP Spec Hard IP Spec Hard IP Spec Hard IP

Posted

Memory Write or

Message

Request

N

(11)

Y/N

(12)

N

(11)

N

(12)

YYYY

Y/N

(11)

Y

(12)

N

(11)

N

(12)

Y/N

(11)

Y

(12)

N

(11)

N

(12)

Loading...

Loading...