2–12 Chapter 2: Getting Started

Qsys Design Flow

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

11. On the Func 0 Device tab, under PCI Express/PCI Capabilities for Func 0 turn

Function Level Reset (FLR) On.

12. Specify the Link settings listed in Table 2–16.

13. On the Func0 MSI tab, for Number of MSI messages requested, select 4.

14. On the Func0 MSI-X tab, turn Implement MSI-X turned off.

15. Click the Finish button.

16. To rename the Cyclone V hard IP for PCI Express, in the Name column of the

System Contents tab, right-click on the component name, select Rename, and

type

DUT

r

Specifying the Parameters for the Example Design

Follow these steps to add the Example design for Avalon-Streaming Hard IP for PCI

Express component to your Qsys system.

1. On the Component Library tab, click Example design for Avalon-Streaming

Hard IP for PCI Express and then click Add. The parameter editor appears.

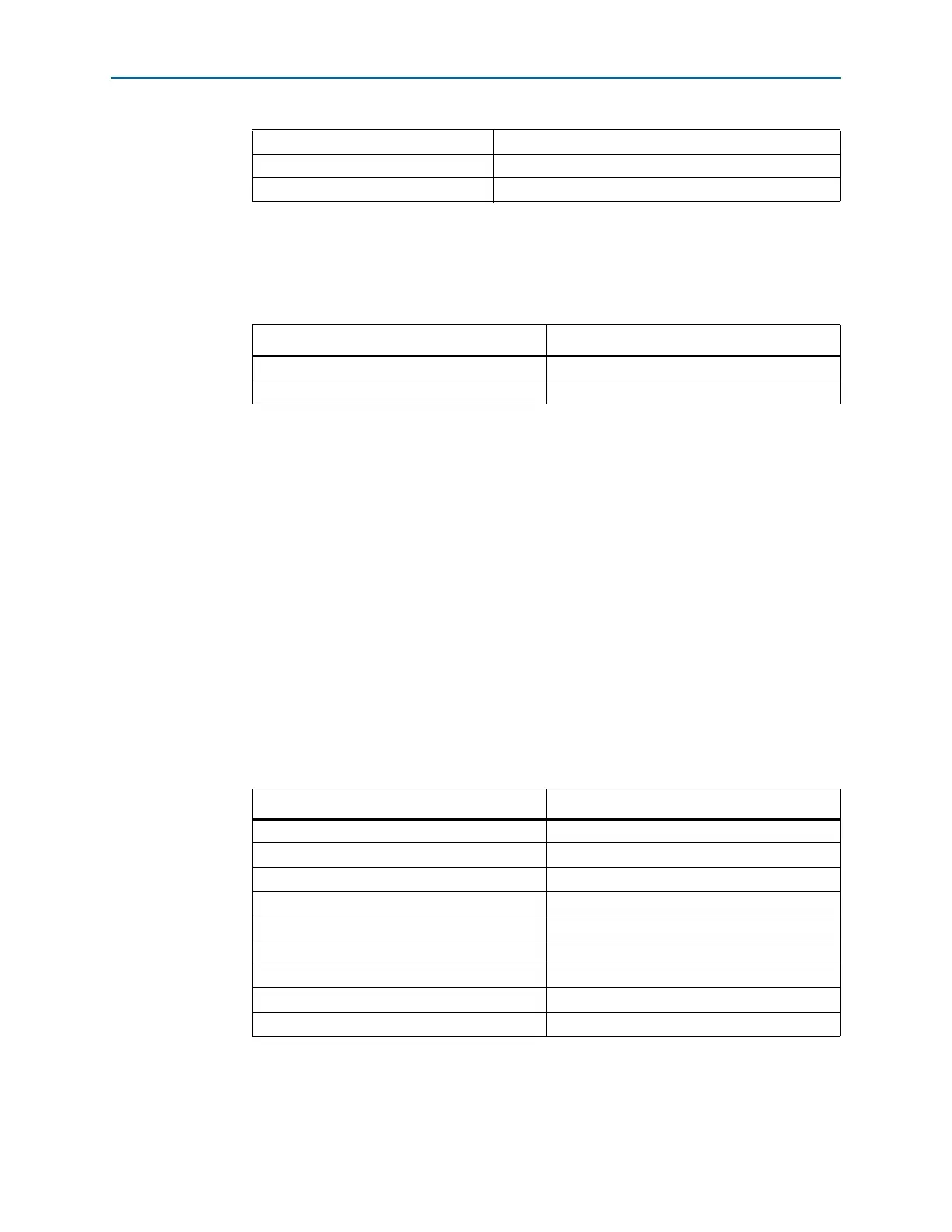

2. Change the parameters to match those of the Gen1 ×4 Endpoint variant by

selecting the parameter values shown in Table 2–17.

3. Click Finish.

Class Code

0x00000000

Subsystem Vendor ID

0x00000000

Subsystem Device ID

0x00000000

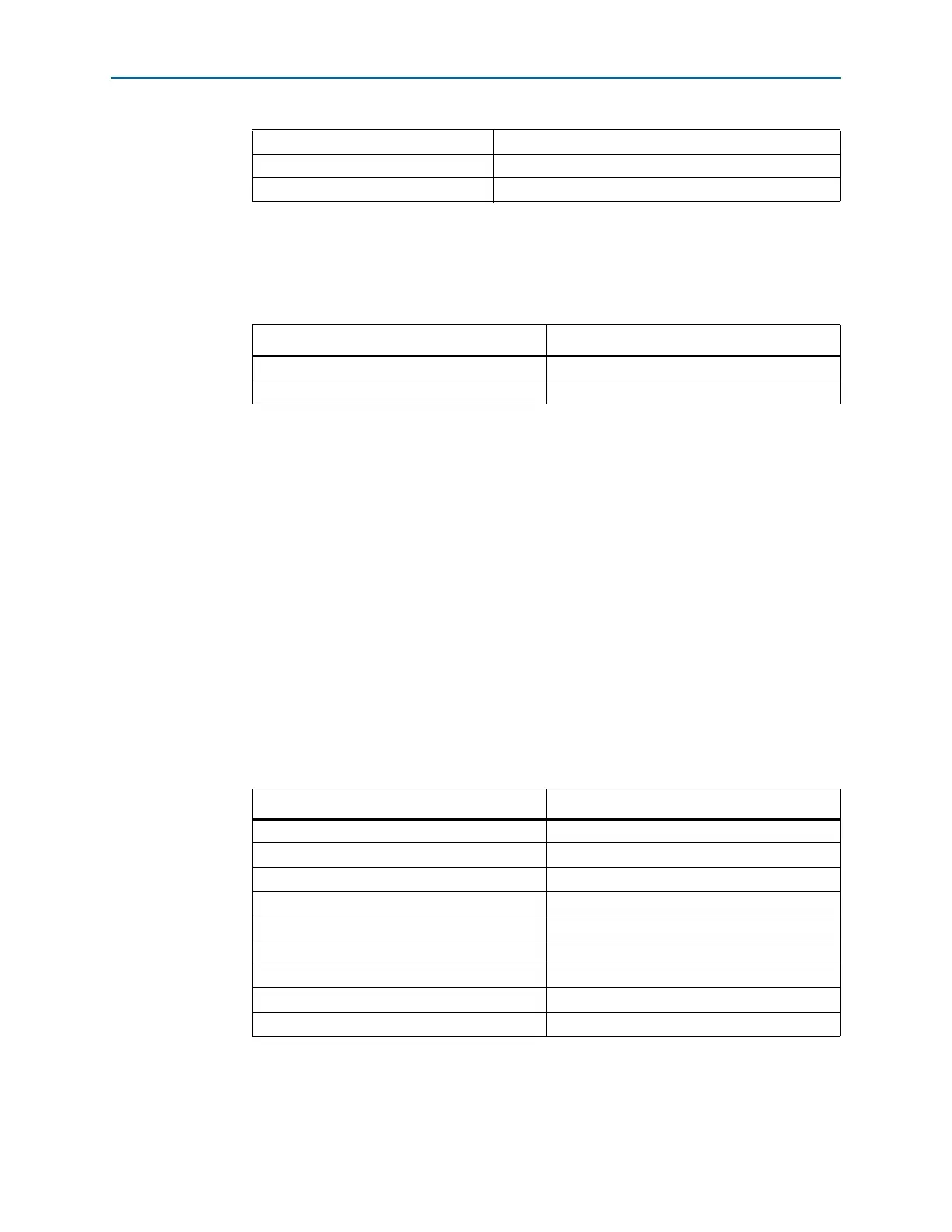

Table 2–16. Link Capabilities

Parameter Value

Data link layer active reporting Off

Surprise down reporting Off

Table 2–17. Parameters for the Example Design

Parameter Value

Targeted device family Cyclone V

Lanes ×4

Lane rate Gen1 (2.5 Gbps)

Application Clock Rate 125 MHz

Port type Native Endpoint

Application interface Avalon-ST 64-bit

Tags supported 32

Maximum payload size 256

Number of functions 1

Table 2–15. Device Identification Registers for Func0 (Part 2 of 2)

Loading...

Loading...