Chapter 5: IP Core Interfaces 5–11

Avalon-ST TX Interface

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

Avalon-ST Packets to PCI Express TLPs

The following figures illustrate the mappings between Avalon-ST packets and PCI

Express TLPs. These mappings apply to all types of TLPs, including posted,

non-posted, and completion TLPs. Message TLPs use the mappings shown for four

dword headers. TLP data is always address-aligned on the Avalon-ST interface

whether or not the lower dwords of the header contains a valid address as may be the

case with TLP type message request with data payload.

f For additional information about TLP packet headers, refer to Appendix A,

Transaction Layer Packet (TLP) Header Formats and Section 2.2.1 Common Packet

Header Fields in the PCI Express Base Specification 2.1.

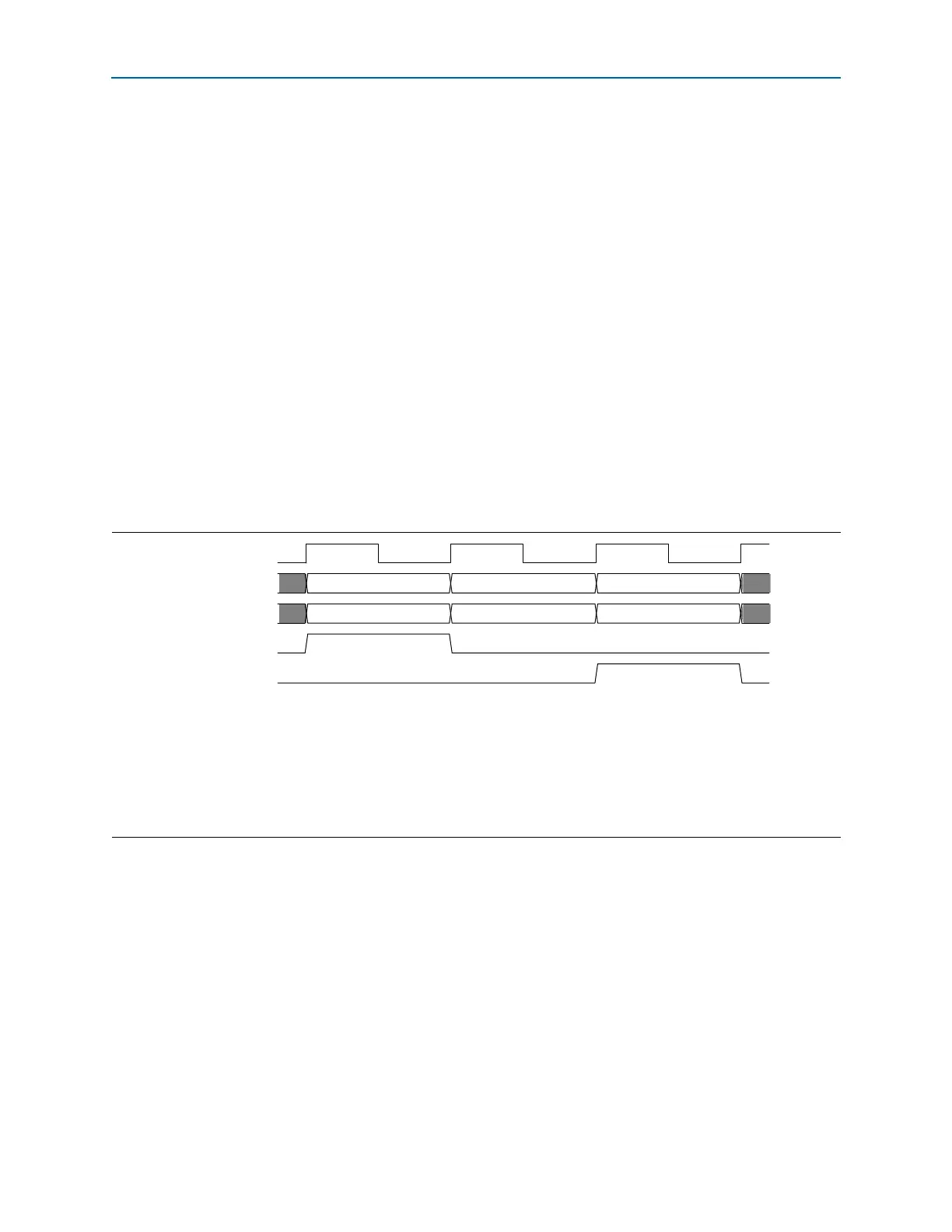

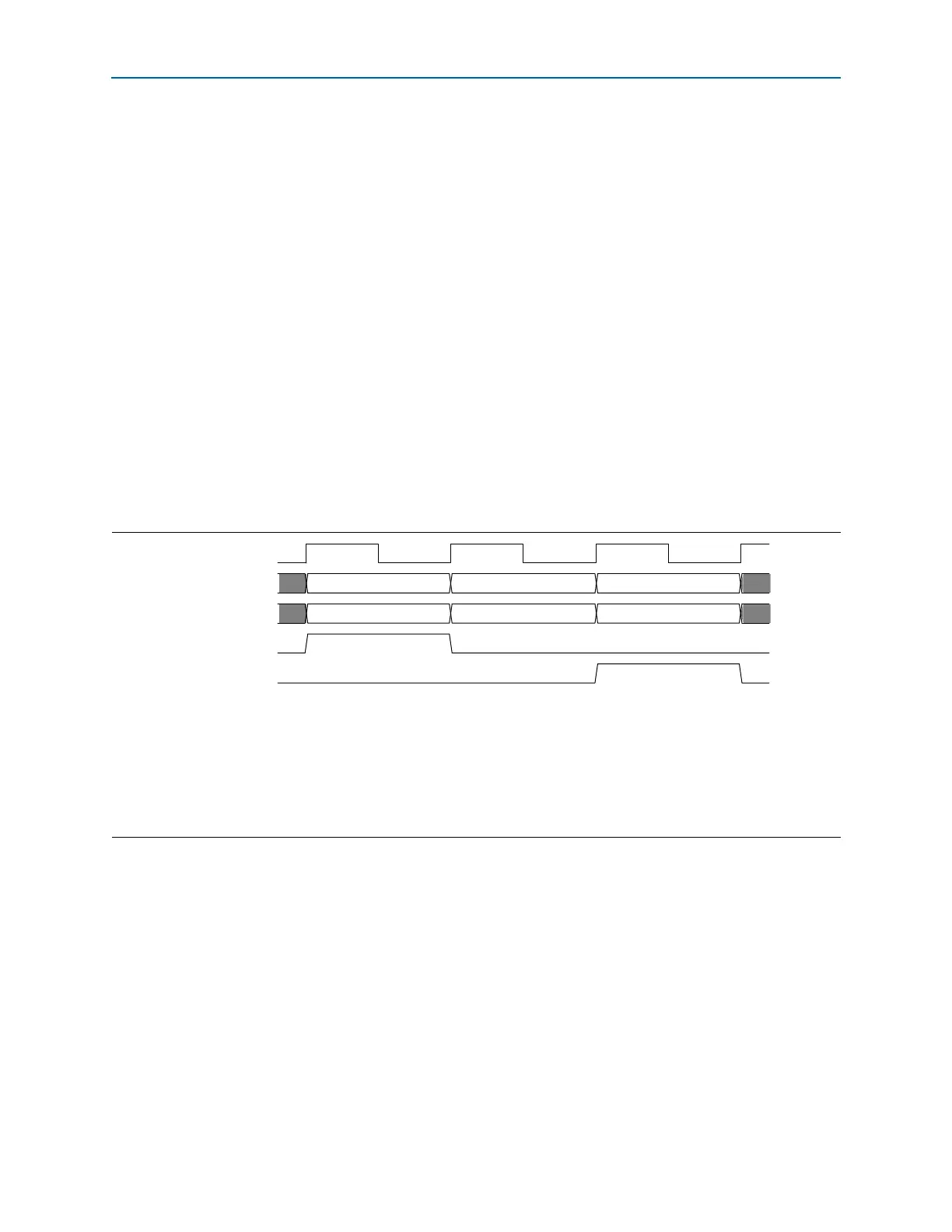

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface

Figure 5–9 illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for 3 dword header TLPs with non-qword aligned addresses with a 64-bit bus.

(Figure 5–2 on page 5–5 illustrates the storage of non-qword aligned data.)

Non-qword aligned addresses occur when address[2] is set. When address[2] is set,

tx_st_data[63:32]

contains

Data0

and

tx_st_data[31:0]

contains dword

header2

.

Figure 5–9. 64-Bit Avalon-ST tx_st_data Cycle Definition for 3-Dword Header TLP with Non-Qword Aligned Address

Notes to Figure 5–9:

(1) Header0 ={pcie_hdr_byte0, pcie_hdr _byte1, pcie_hdr _byte2, pcie_hdr _byte3}

(2) Header1 = {pcie_hdr_byte4, pcie_hdr _byte5, header pcie_hdr byte6, pcie_hdr _byte7}

(3) Header2 = {pcie_hdr _byte8, pcie_hdr _byte9, pcie_hdr _byte10, pcie_hdr _byte11}

(4) Data0 = {pcie_data_byte3, pcie_data_byte2, pcie_data_byte1, pcie_data_byte0}

(5) Data1 = {pcie_data_byte7, pcie_data_byte6, pcie_data_byte5, pcie_data_byte4}

(6) Data2 = {pcie_data_byte11, pcie_data_byte10, pcie_data_byte9, pcie_data_byte8}

coreclkout

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1 Data0 Data2

Header0 Header2 Data1

Loading...

Loading...