November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

1. Datasheet

This document describes the Altera

®

Cyclone

®

V Hard IP for PCI Express

®

. PCI

Express is a high-performance interconnect protocol for use in a variety of

applications including network adapters, storage area networks, embedded

controllers, graphic accelerator boards, and audio-video products. The PCI Express

protocol is software backwards-compatible with the earlier PCI and PCI-X protocols,

but is significantly different from its predecessors. It is a packet-based, serial,

point-to-point interconnect between two devices. The performance is scalable based

on the number of lanes that is implemented. Altera offers a configurable hard IP

block in Cyclone V devices for both Endpoints and Root Ports that complies with the

PCI Express Base Specification 2.1. Using a configurable hard IP block, rather than

programmable logic, saves significant FPGA resources. hard IP block is available in

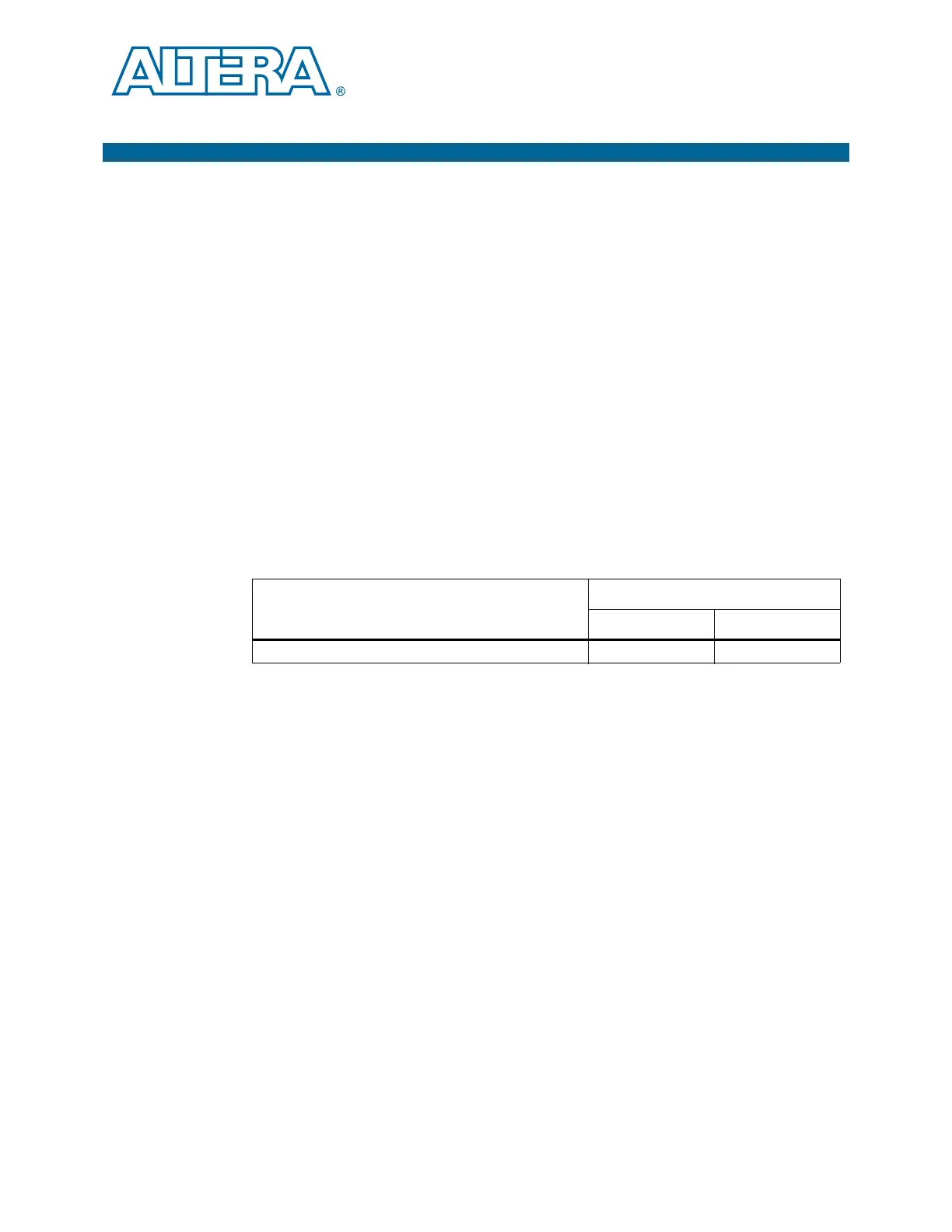

×1 and ×4 configurations.Table 1–1 shows the aggregate bandwidth of a PCI Express

link for the available configurations. The protocol specifies 2.5 giga-transfers per

second for Gen1. Table 1–1 provides bandwidths for a single transmit (TX) or receive

(RX) channel, so that the numbers double for duplex operation. Because the PCI

Express protocol uses 8B/10B encoding, there is a 20% overhead which is included in

the figures in Table 1–1.

f Refer to the PCI Express High Performance Reference Design for more information about

calculating bandwidth for the hard IP implementation of PCI Express in many Altera

FPGAs.

Features

Altera’s Cyclone V Hard IP for PCI Express IP supports the following key features:

■ Complete protocol stack including the Transaction, Data Link, and Physical Layers

is hardened in the device.

■ Multi-function support for up to eight Endpoint functions.

■ Support for ×1 and ×4 configurations.

■ Optional end-to-end cyclic redundancy code (ECRC) generation and checking and

advanced error reporting (AER) for high reliability applications.

■ Qsys support using the Avalon

®

Streaming (Avalon-ST) with a 64- or 128-bit

interface to the Application Layer.

■ Extended credit allocation settings to better optimize the RX buffer space based on

application type.

Table 1–1. PCI Express Throughput

Link Width

×1 ×4

PCI Express Gen1 Gbps (1.x compliant) 2.5 10

November 2011

1101

Loading...

Loading...