Chapter 1: Datasheet 1–5

IP Core Verification

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive

validation of the Cyclone V Hard IP Core for PCI Express.

Altera’s simulation environment uses multiple testbenches that consist of

industry-standard BFMs driving the PCI Express link interface. A custom BFM

connects to the application-side interface.

Altera performs the following tests in the simulation environment:

■ Directed and pseudo random stimuli are applied to test the Application Layer

interface, Configuration space, and all types and sizes of TLPs.

■ Error injection tests that inject errors in the link, TLPs, and Data Link Layer

Packets (DLLPs), and check for the proper responses

■ PCI-SIG

®

Compliance Checklist tests that specifically test the items in the checklist

■ Random tests that test a wide range of traffic patterns

Performance and Resource Utilization

Because the IP core is implemented in hardened logic, it uses less than 1% of

Cyclone V resources.

Depending on the speed of the variant, soft calibration logic may be required, with

more logic required for more lanes. The amount of additional logic for calibration for

the transceiver modules is pending characterization of the Cyclone V device.

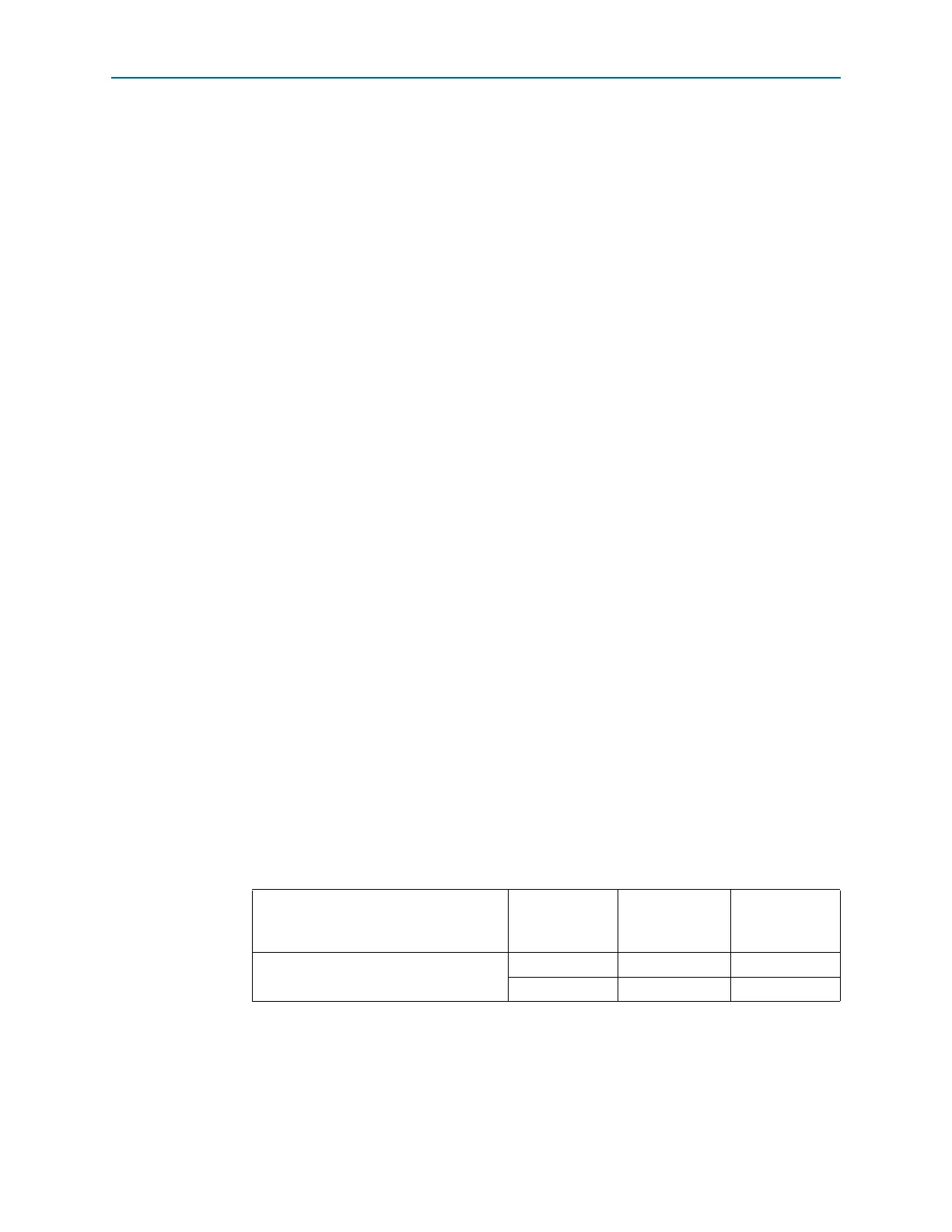

Recommended Speed Grades

Table 1–4 lists the recommended speed grades for the supported link widths and

Application Layer clock frequencies. The speed grades listed are the only speed

grades that close timing. Altera recommends setting the Quartus II Analysis &

Synthesis Settings Optimization Technique to Speed.

h Refer to “Setting Up and Running Analysis and Synthesis in Quartus II Help for

information about optimizing synthesis.

f Refer to Area and Timing Optimization in volume 2 of the Quartus II Handbook for more

information about how to effect the Optimization Technique setting.

f For details on installation, refer to the Altera Software Installation and Licensing Manual.

Table 1–4. Device Family Link Width Application Frequency Recommended Speed Grades

Link Speed Link Width

Application

Clock

Frequency (MHz)

Recommended

Speed Grades

Gen1–2.5 Mbps

×1 125 –4, –5, –6

×4 125 –4, –5, –6

Notes to Table 1–4:

(1) This is a power-saving mode of operation.

(2) Final results pending characterization by Altera for speed grades -2, -3, and -4. Refer to the .fit.rpt file generated

by the Quartus II software.

Loading...

Loading...