4–2 Chapter 4: IP Core Architecture

Key Interfaces

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

This chapter provides an overview of the architecture of the Cyclone V Hard IP for

PCI Express. It includes the following sections:

■ Key Interfaces

■ Protocol Layers

■ Multi-Function Support

Key Interfaces

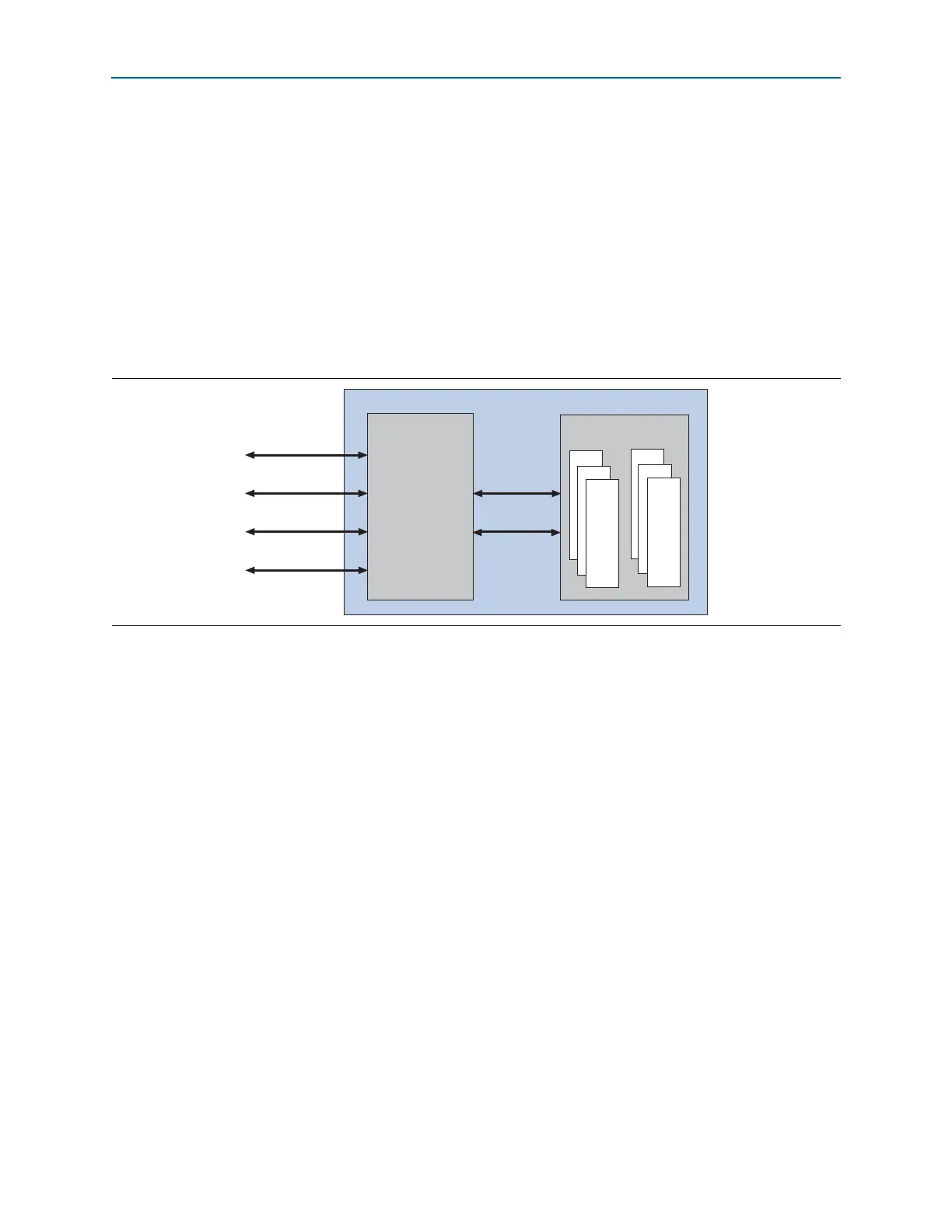

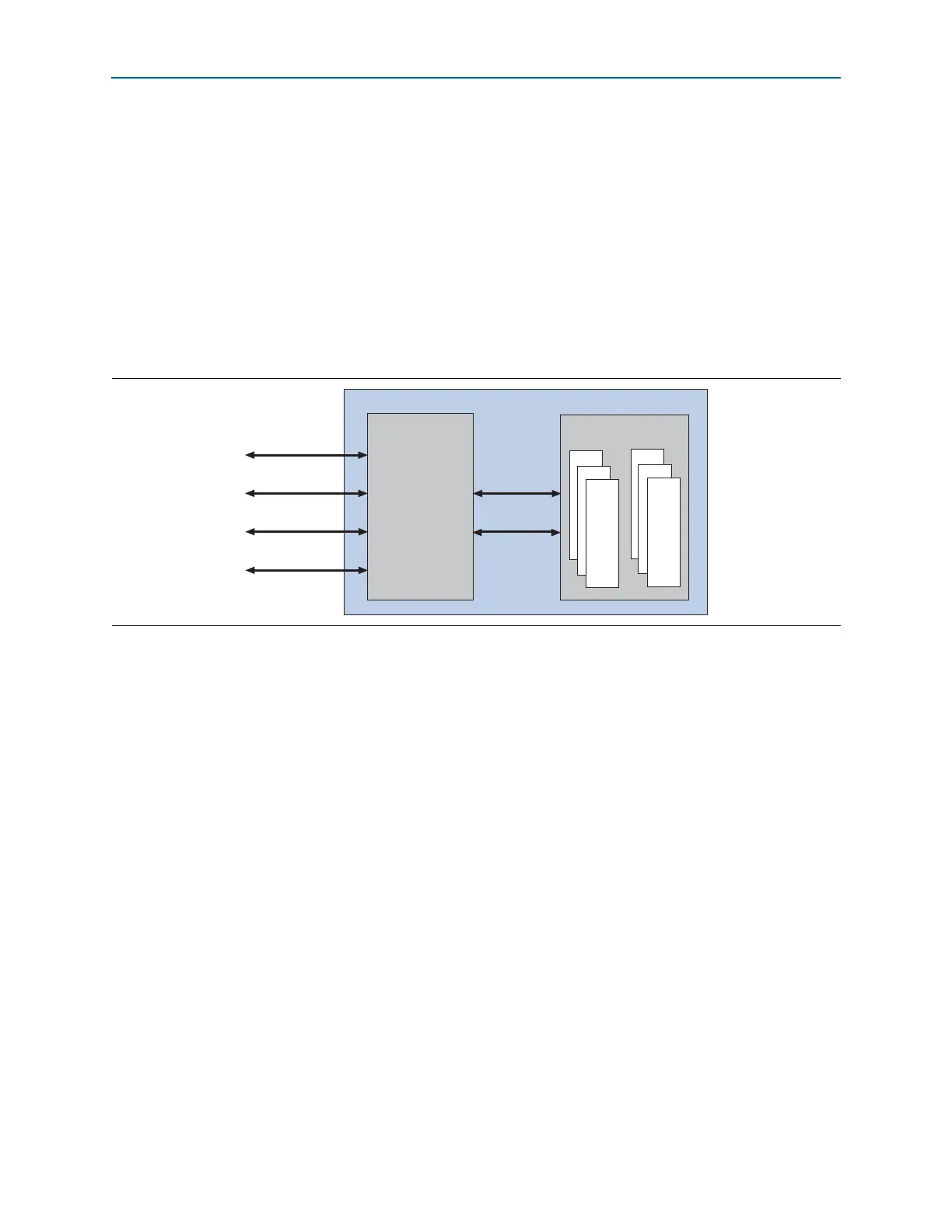

The following sections introduce the functionality of the interfaces shown in

Figure 4–1.

.

Avalon-ST Interface

An Avalon-ST interface connects the Application Layer and the Transaction Layer.

This is a point-to-point, streaming interface designed for high throughput

applications. The Avalon-ST interface includes the RX and TX datapaths.

f For more information about the Avalon-ST interface, including timing diagrams, refer

to the Avalon Interface Specifications.

RX Datapath

The RX datapath transports data from the Transaction Layer to the Application

Layer’s Avalon-ST interface. Masking of non-posted requests is partially supported.

Refer to the description of the

rx_st_mask

signal for further information about

masking. For more detailed information about the RX datapath, refer to “Avalon-ST

RX Interface” on page 5–3.

TX Datapath

The TX datapath transports data from the Application Layer's Avalon-ST interface to

the Transaction Layer. The Hard IP provides credit information to the Application

Layer for posted headers, posted data, non-posted headers, non-posted data,

completion headers and completion data.

Figure 4–1. Block Diagram

PMAPCS

Hard IP for

PCI Express

Altera FPGA

Avalon-ST

Interrupts

Clocks and Reset

LMI

PIPE Interface

Transceiver

Reconfiguration

PHY IP Core for

PCI Express (PIPE)

Loading...

Loading...