Chapter 2: Getting Started 2–9

Qsys Design Flow

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

Qsys Design Flow

This section guides you through the steps necessary to customize the Cyclone V Hard

IP for PCI Express and run the example testbench in Qsys. It includes the following

steps:

■ Customizing the Endpoint in Qsys

■ Understanding the Files Generated

■ Generating the Simulation Model Using Qsys

■ Compiling the Design in the Qsys Design Flow

■ Modifying the Example Design

Customizing the Endpoint in Qsys

This section begins with the steps necessary to customize the Cyclone V Hard IP for

PCI Express. This section also guides you through steps to connect the chaining DMA

component testbench.

f For further details about the parameter settings, refer to Chapter 3, Parameter

Settings.

Follow these steps to instantiate the Cyclone V Hard IP for PCI Express and chaining

DMA example design using the Qsys design flow:

1. Create a directory for your project. This example uses <working_dir>/pcie_qsys.

2. To start Qsys from the Quartus II software, on the File menu click New.

3. In the New dialog box, click Qsys System File, then click OK. Qsys appears.

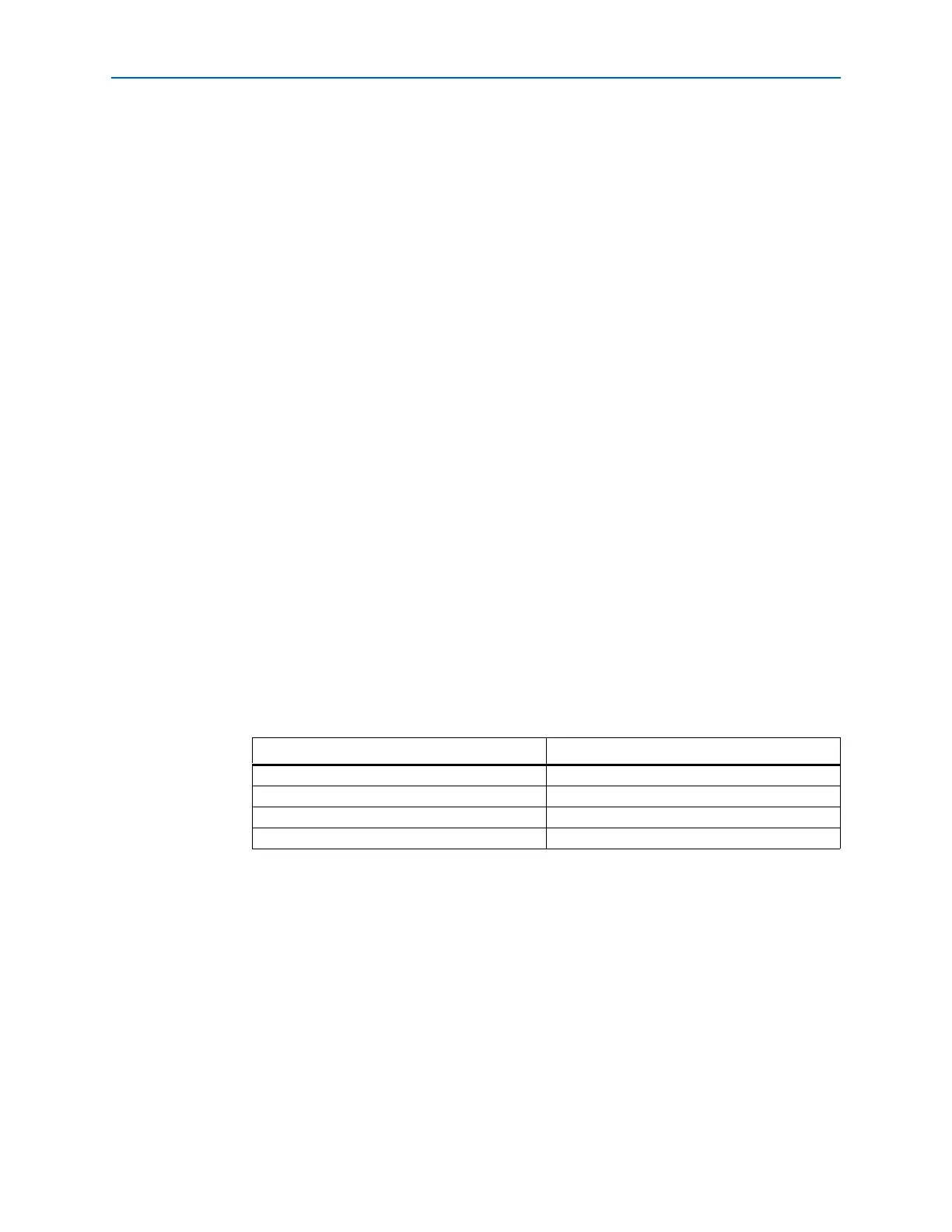

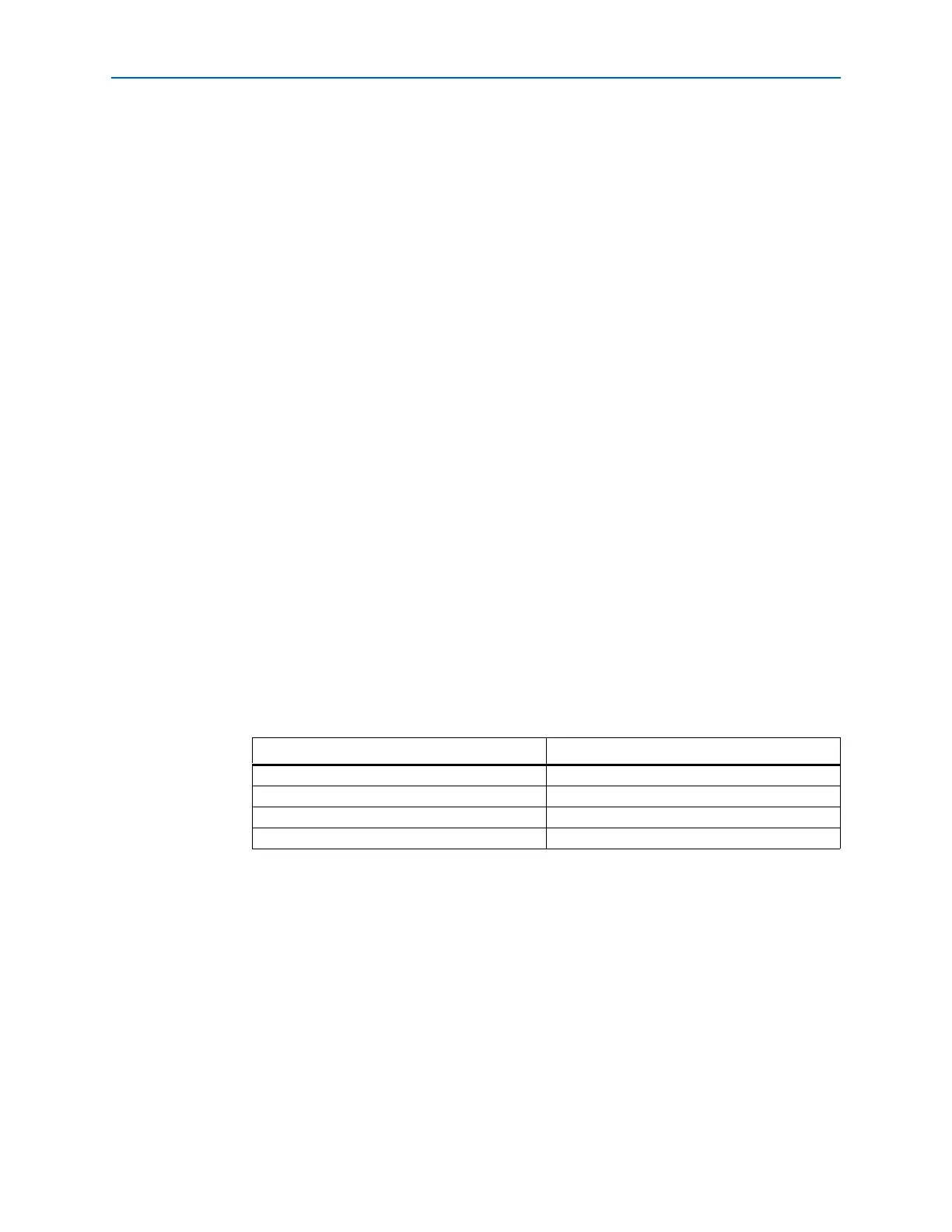

4. On the Project Settings tab specify the settings listed in Table 2–8

5. On the Component Library tab, type the following text string in the search box:

PCI Ex r

Qsys filters the component library and shows all components matching the text

string you entered.

6. Click on Cyclone V Hard IP for PCI Express and then click the +Add button. The

parameter editor appears.

Table 2–8. Project Settings Parameters

Parameter Value

Device family Cyclone V

Clock crossing adapter type Handshake

Limit interconnect pipeline stages to

(1)

0

Generation ID 0

Note to Table 2–8:

(1) This setting applies to designs that include Avalon-MM interfaces.

Loading...

Loading...