5–18 Chapter 5: IP Core Interfaces

Interrupts for Root Ports

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

Interrupts for Root Ports

Table 5–9 describes the signals available to a Root Port to handle interrupts.

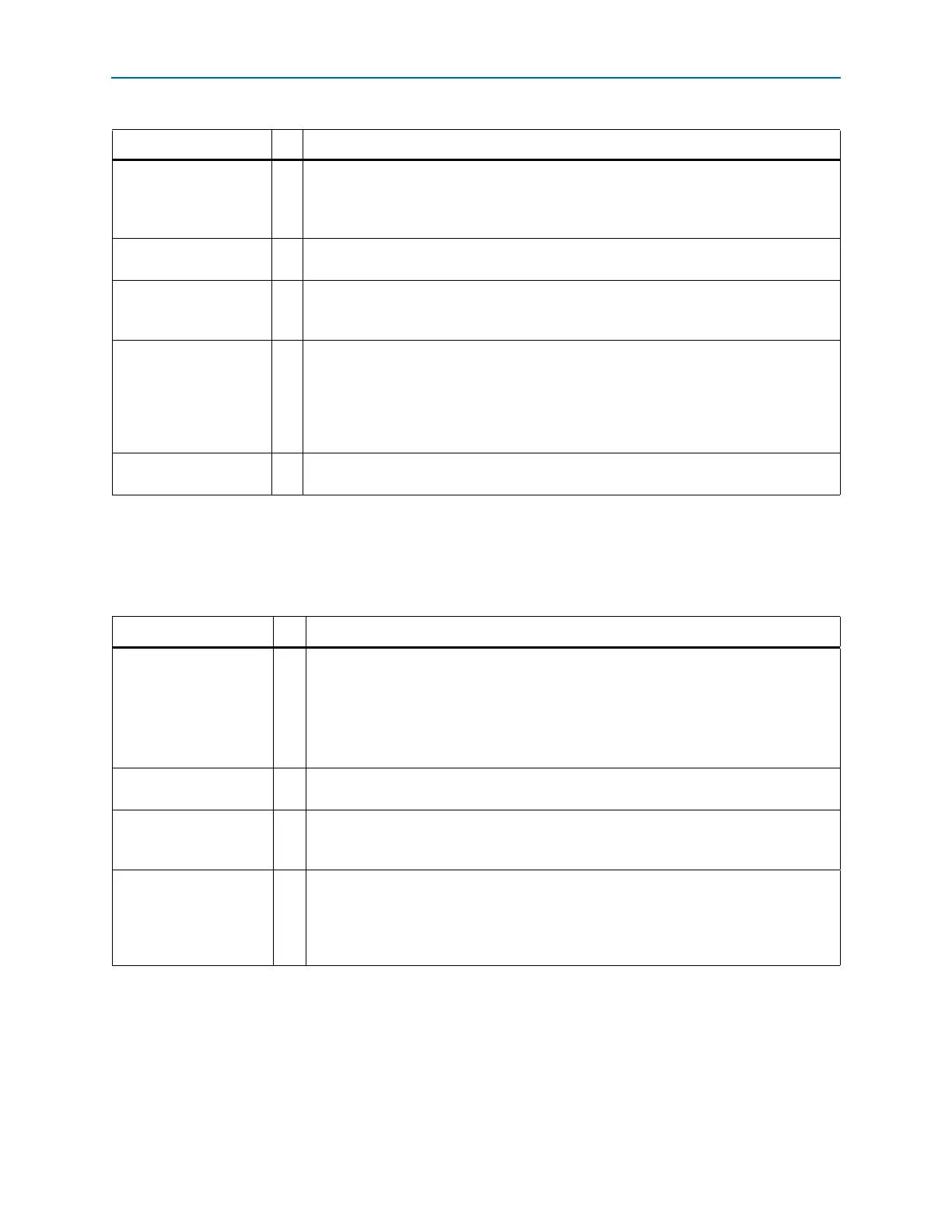

tl_app_msi_num[4:0]

I

MSI number of the Application Layer. This signal provides the low order message data bits

to be sent in the message data field of MSI messages requested by tl_

app_msi_req

. Only

bits that are enabled by the MSI Message Control register apply. Refer to Table 5–15 on

page 5–27 for more information.

tl_app_msi_func

[2:0]

I

Indicates which function is asserting an interrupt with 0 corresponding to function 0, 1

corresponding to function 1, and so on.

tl_app_int<a>_sts

I

Controls legacy interrupts. Assertion of tl_

app_int<a>_sts

causes an Assert_INTA

message TLP to be generated and sent upstream. Deassertion of tl_

app_int<a>_sts

causes a Deassert_INTA message TLP to be generated and sent upstream.

tl_app_int<a>_ack

O

This signal is the acknowledge for tl_

app_int<a>_sts

. This signal is asserted for at least

one cycle either when the

Assert_INTA

message TLP has been transmitted in response to

the assertion of the tl_

app_int<a>_sts

signal or when the

Deassert_INTA

message

TLP has been transmitted in response to the deassertion of the tl_

app_int<a>_sts

signal. Refer to Figure 10–5 on page 10–4 and Figure 10–6 on page 10–4 for timing

information.

tl_app_int<a>_func_

num[2:0]

O

Indicates which function is asserting an interrupt with 0 corresponding to function 0, 1

corresponding to function 1, and so on.

Table 5–8. Interrupt Signals for Endpoints (Part 2 of 2)

Signal I/O Description

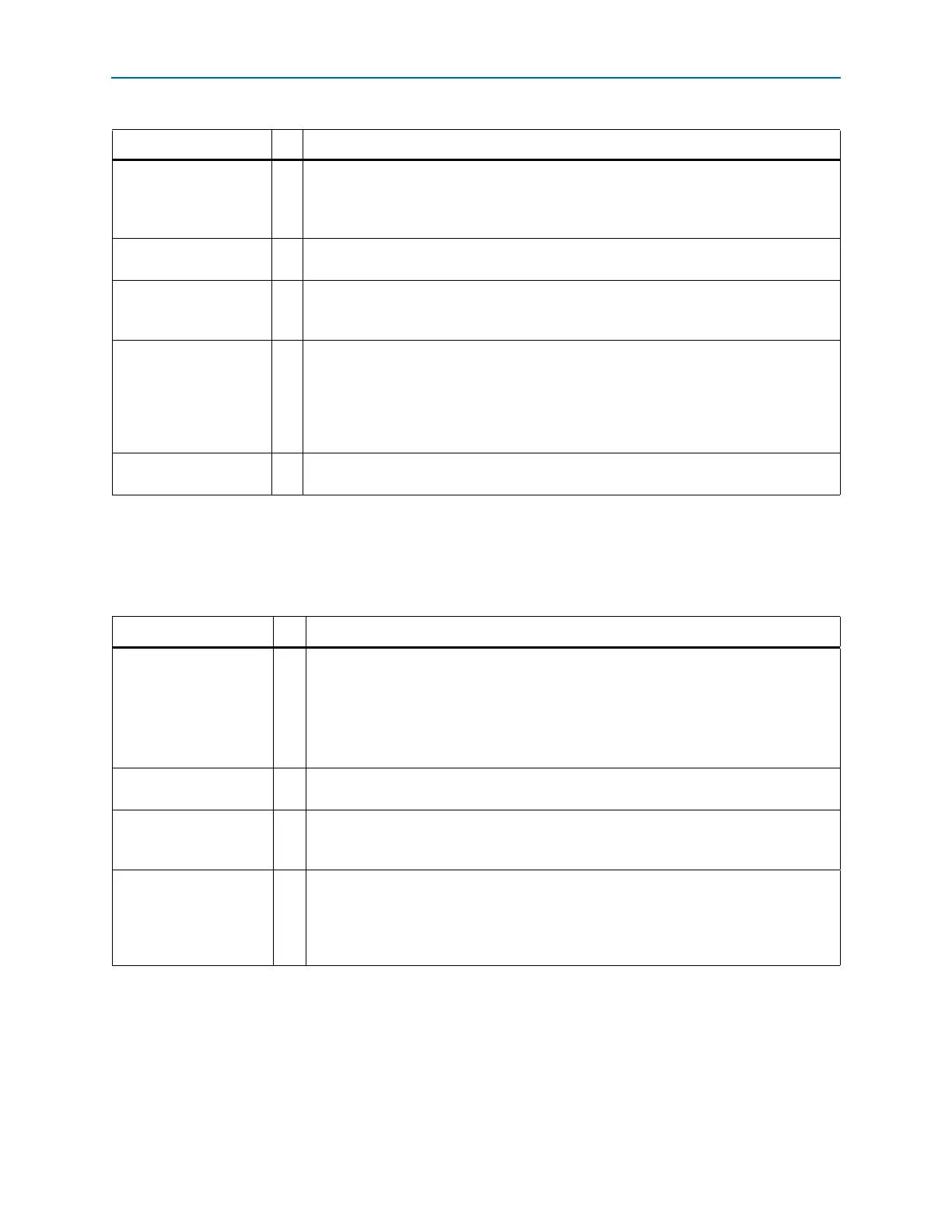

Table 5–9. Interrupt Signals for Root Ports

Signal I/O Description

int_status[3:0]

O

These signals drive legacy interrupts to the Application Layer as follows:

■ int_status[0]: interrupt signal A

■ int_status[1]: interrupt signal B

■ int_status[2]: interrupt signal C

■ int_status[3]: interrupt signal D

aer_msi_num[4:0]

I

Advanced error reporting (AER) MSI number. This signal is used by AER to determine the

offset between the base message data and the MSI to send.

pex_msi_num[4:0]

I

Power management MSI number. This signal is used by power management and hot plug

or both to determine the offset between the base message interrupt number and the

message interrupt number to send through MSI.

serr_out

O

System Error: This signal only applies to Root Port designs that report each system error

detected, assuming the proper enabling bits are asserted in the

Root

Control

register

and the

Device

Control

register. If enabled,

serr_out

is asserted for a single clock

cycle when a system error occurs. System errors are described in the PCI Express Base

Specification 1.1 or 2.0. in the

Root

Control register

.

Loading...

Loading...