2–6 Chapter 2: Getting Started

MegaWizard Plug-In Manager Design Flow

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

16. Under the Base and Limit Registers heading, disable both the Input/Output and

Prefetchable memory options. (These options are for Root Ports.)

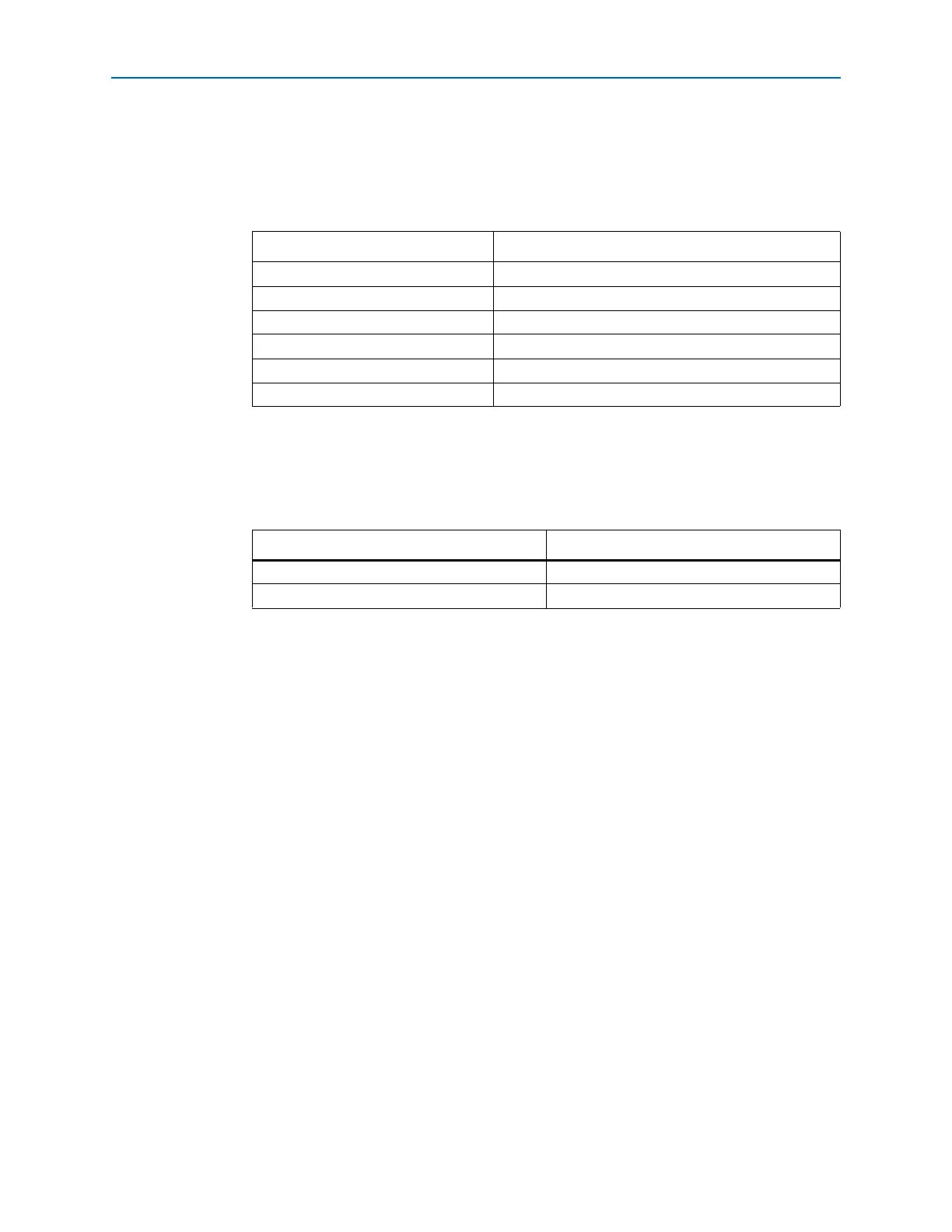

17. Specify the Device ID Registers for Func0 listed in Table 2–6.

18. On the Func 0 Device tab, under PCI Express/PCI Capabilities for Func 0 turn

Function Level Reset (FLR) On.

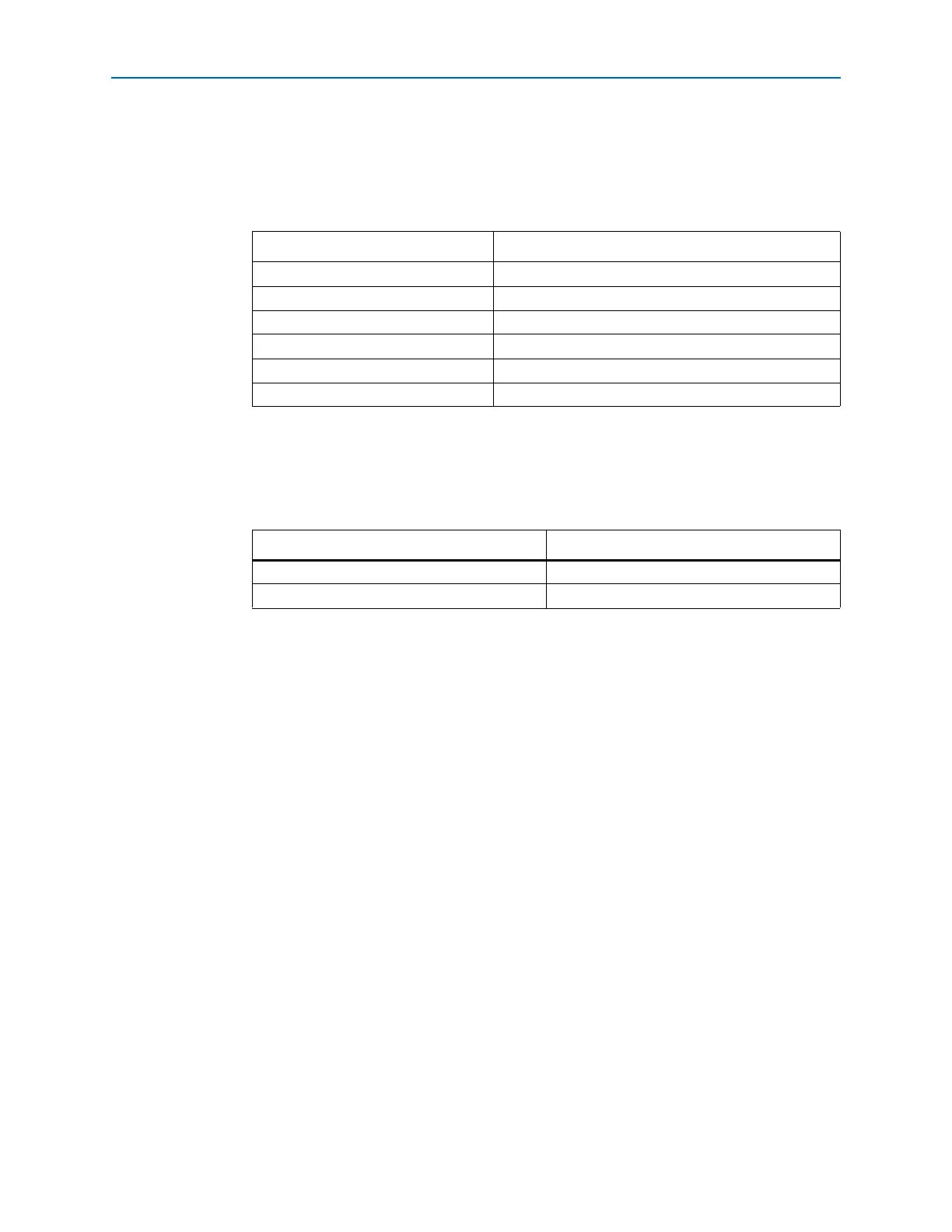

19. Table 2–7 lists settings for the Func0 Link tab.

20. On the Func0 MSI tab, for Number of MSI messages requested, select 4.

21. On the Func0 MSI-X tab, turn Implement MSI-X off.

22. Click Finish. The Generation dialog box appears.

23. Turn on Generate Example Design to generate the Endpoint, testbench, and

supporting files.

24. Click Exit.

25. Click Yes if you are prompted to add the Quartus II IP File (.qip) to the project.

The .qip is a file generated by the parameter editor contains all of the necessary

assignments and information required to process the IP core in the Quartus II

compiler. Generally, a single .qip file is generated for each IP core.

Understanding the Files Generated

Figure 2–2 illustrates the directory structure created for this design after you generate

the Cyclone V Hard IP for PCI Express. Generation creates three directories:

■ <working_dir>/<variant_name> includes the files for synthesis.

■ <working_dir>/<variant_name>_sim/altera_pcie_cv_hip_ast includes the

simulation files.

■ <working_dir>/<variant_name>_example_design/altera_pcie_cv_hip_ast contains

a Qsys system that connects the Endpoint variant to a chaining DMA design

example for verification.

Table 2–6. Device ID Registers for Func0

Register Name Value

Vendor ID

0x00000000

Device ID

0x00000001

Revision ID

0x00000001

Class Code

0x00000000

Subsystem Vendor ID

0x00000000

Subsystem Device ID

0x00000000

Table 2–7. Link Capabilities

Parameter Value

Data link layer active reporting Off

Surprise down reporting Off

Loading...

Loading...