5–20 Chapter 5: IP Core Interfaces

Transaction Layer Configuration Space Signals

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

Transaction Layer Configuration Space Signals

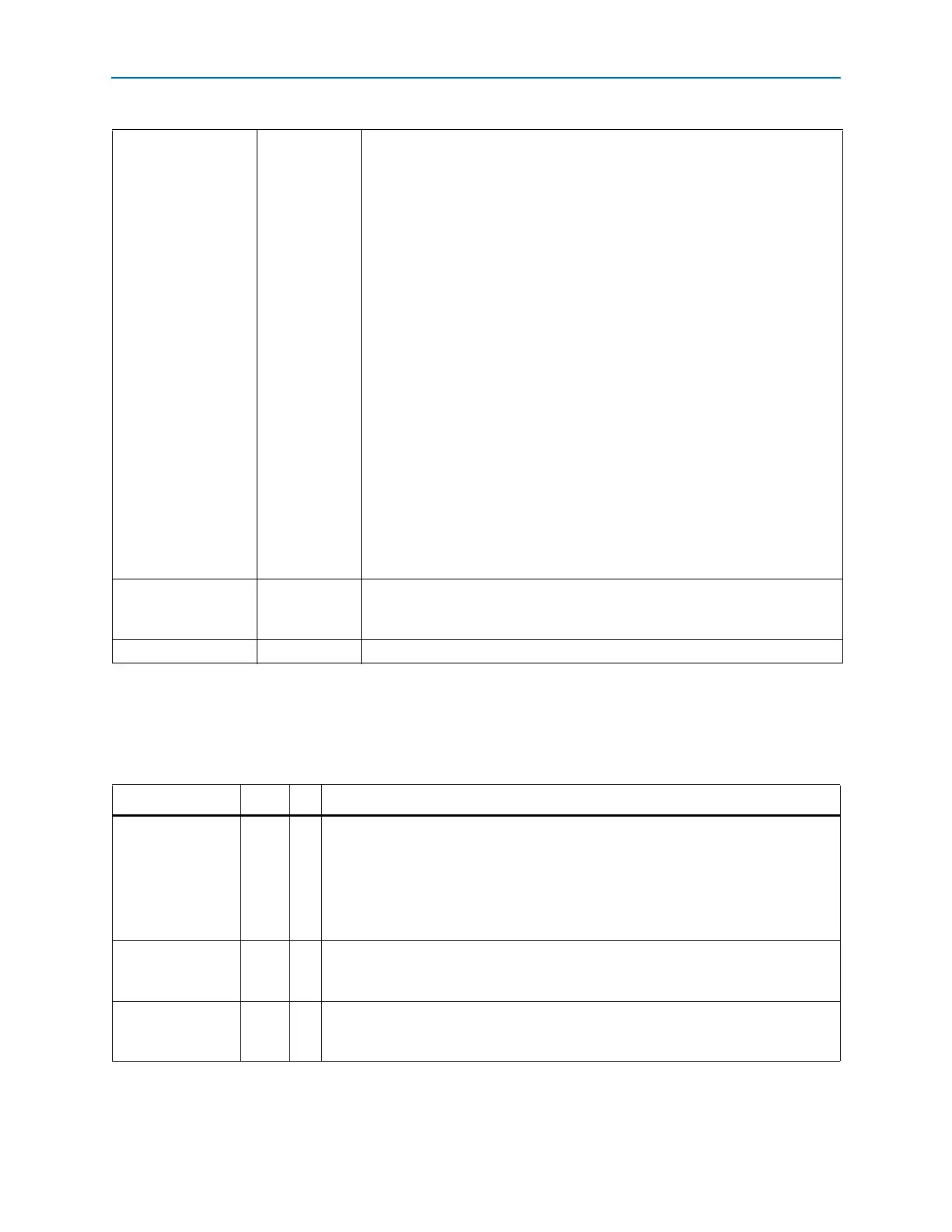

Table 5–11 describes the Transaction Layer Configuration Space signals.

cpl_err[6:0]

(continued)

■

cpl_err[5]

: Unsupported Request error for non-posted TLP. The Application

Layer asserts this signal to respond to a non-posted request with an

Unsupported Request (UR) completion. In this case, the Application Layer

sends a completion packet with the Unsupported Request status back to the

requestor, and asserts this error signal. The Hard IP automatically sets the

error status bits in the Configuration Space Register and sends error

messages in accordance with the

PCI Express Base Specification. Many

cases of Unsupported Requests are detected and reported internally by the

Transaction Layer. For a list of these cases, refer to “Transaction Layer Errors”

on page 12–3.

■

cpl_err[6]

: Log header. If header logging is required, this bit must be set in

every cycle in which any of

cpl_err[2]

,

cpl_err[3]

,

cpl_err[4]

, or

cpl_err[5]

is asserted. The Application Layer presents the header to the

Hard IP by writing the following values to the following 4 registers using LMI

before asserting

cpl_err[6]

:

■ lmi_addr: 12'h81C,

lmi_din

:

err_desc_func0[127:96]

■ lmi_addr: 12'h820,

lmi_din

:

err_desc_func0[95:64]

■ lmi_addr: 12'h824,

lmi_din

:

err_desc_func0[63:32]

■ lmi_addr: 12'h828,

lmi_din

:

err_desc_func0[31:0]

Refer to the “LMI Signals” on page 5–27 for more information about LMI

signalling.

cpl_pending

I

Completion pending. The Application Layer must assert this signal when a

master block is waiting for completion, for example, when a transaction is

pending.

cpl_err_func[2:0]

I Specifies the function number of the completion error.

Table 5–10. Completion Signals for the Avalon-ST Interface (Part 2 of 2)

Signal I/O Description

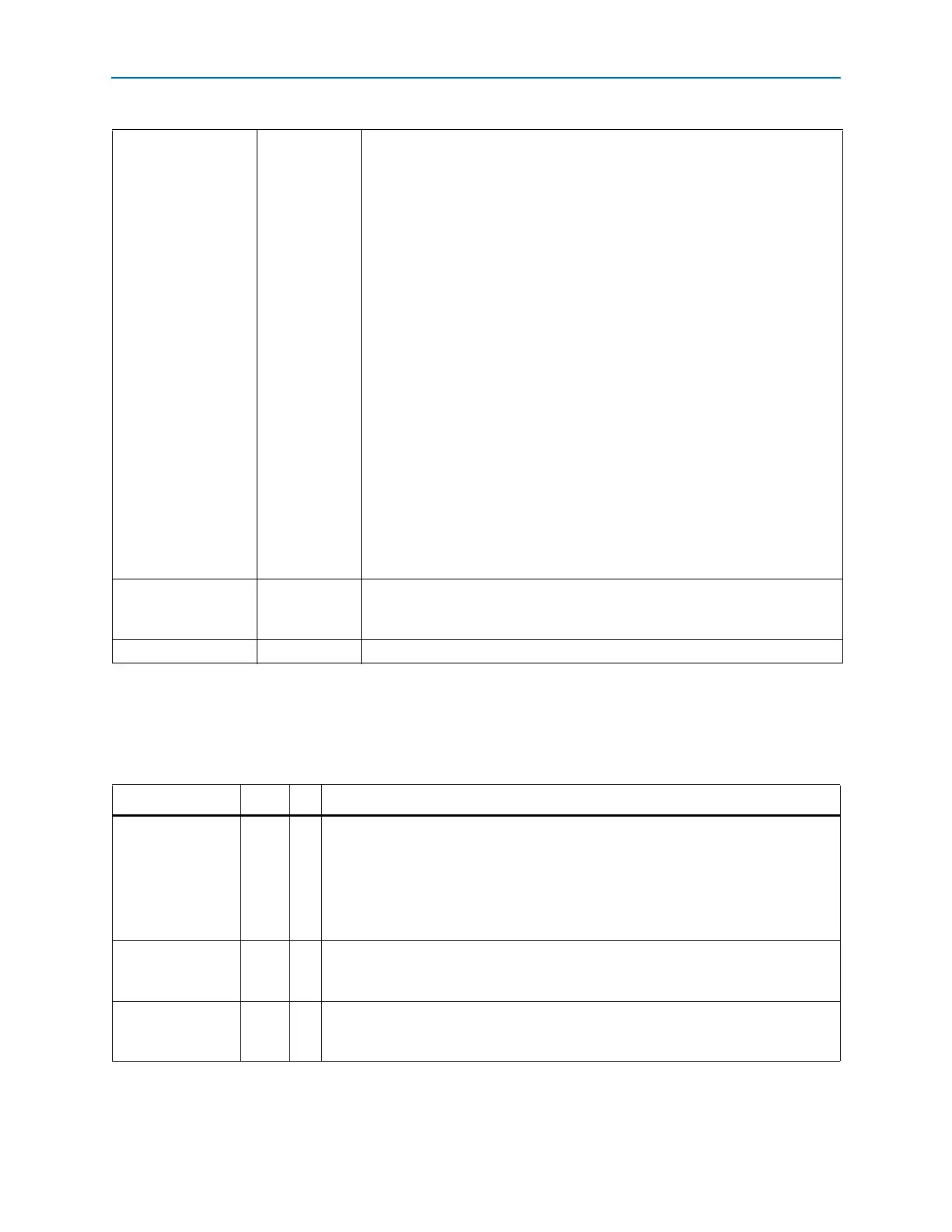

Table 5–11. Configuration Space Signals (Hard IP Implementation) (Part 1 of 2)

Signal Width Dir Description

tl_cfg_add

70

Address of the register that has been updated. This signal is an index indicating which

Configuration Space register information is being driven onto

tl_cfg_ctl.

The

indexing is defined inTable 5–13 on page 5–24.The index increments on every

pld_clk

cycle. The index consists of the following 2 pars:

■ [6:4] - the function number

■ [3:0] - the register address

tl_cfg_ctl

32 0

The

tl_cfg_ctl

signal is multiplexed and contains the contents of the Configuration

Space registers. The information presented on this bus depends on the

tl_cfg_add

index according toTable 5–13 on page 5–24.

tl_cfg_ctl_wr

10

Write signal. This signal toggles when

tl_cfg_ctl

has been updated (every 8

core_clk

cycles). The toggle edge marks where the

tl_cfg_ctl

data changes. You

can use this edge as a reference to determine when the data is safe to sample.

Loading...

Loading...