Chapter 1: Datasheet 1–3

Release Information

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

Release Information

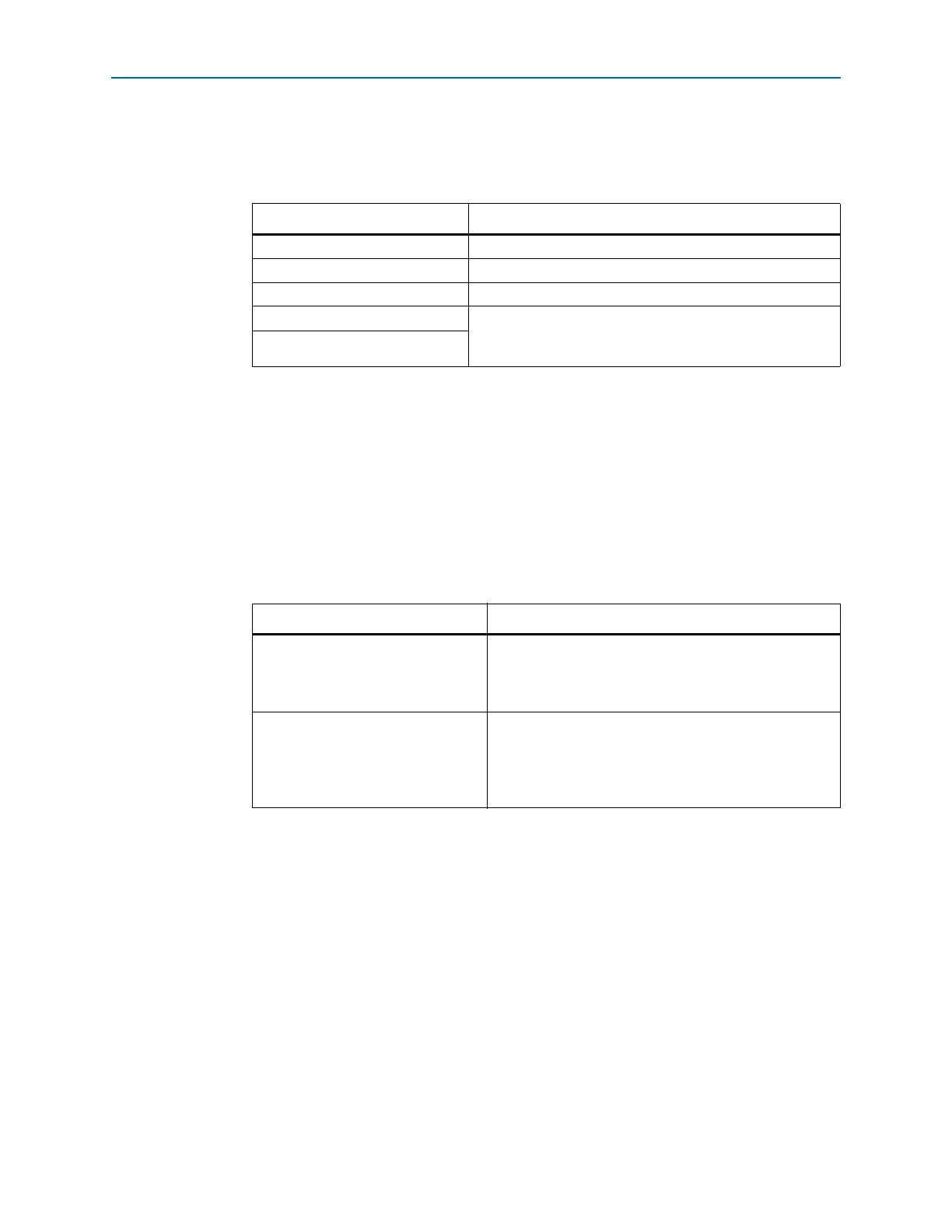

Table 1–2 provides information about this release of the PCI Express Compiler.

Altera verifies that the current version of the Quartus

®

II software compiles the

previous version of each IP core. Any exceptions to this verification are reported in the

MegaCore IP Library Release Notes and Errata. Altera does not verify compilation with

IP core versions older than one release.

Device Family Support

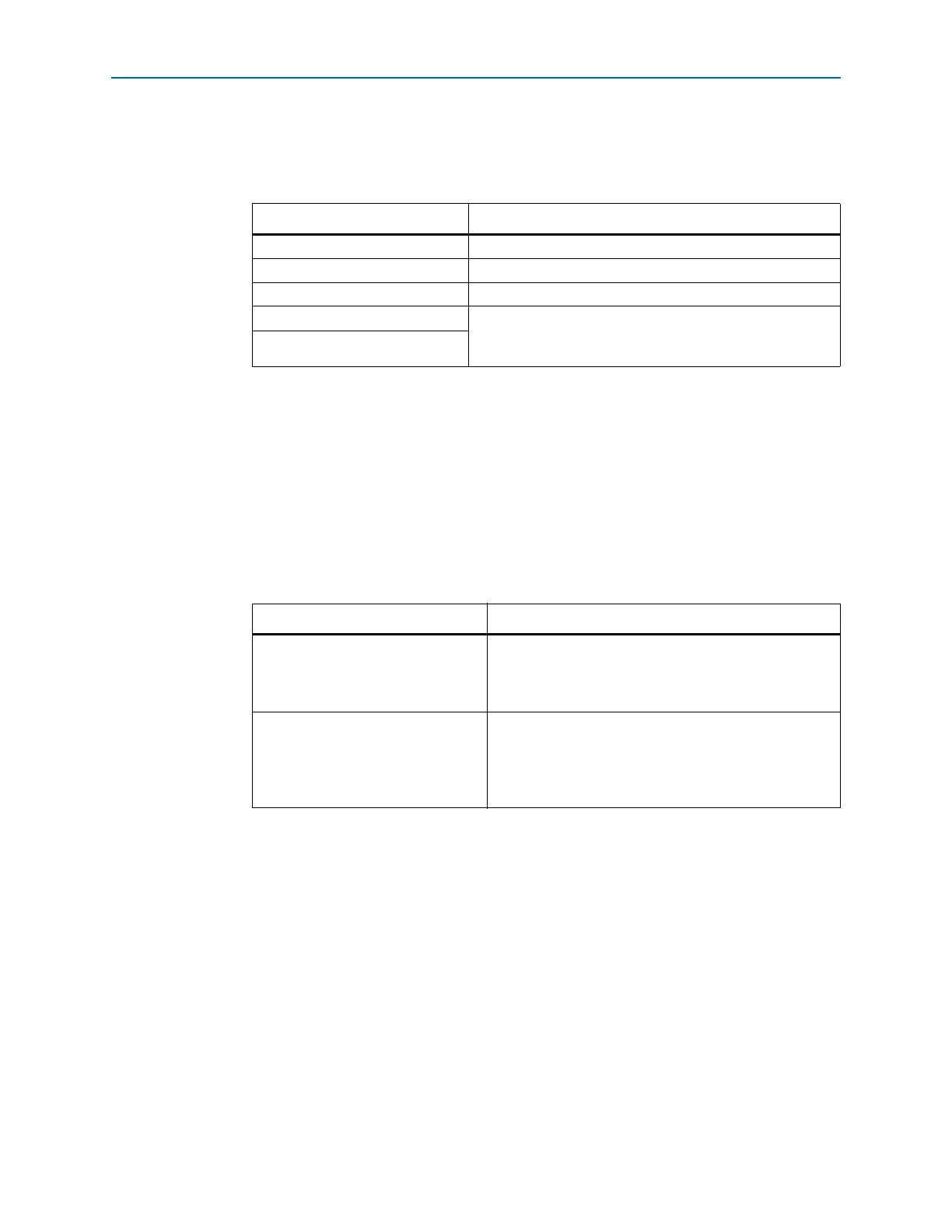

Table 1–3 shows the level of support offered by the Cyclone V Hard IP for PCI

Express.

Configurations

The Cyclone V Hard IP for PCI Express includes a full hard IP implementation of the

PCI Express stack including the following layers:

■ Physical (PHY)

■ Physical Media Attachment (PMA)

■ Physical Coding Sublayer (PCS)

■ Media Access Control (MAC)

■ Data Link Layer (DLL)

■ Transaction Layer (TL)

Table 1–2. PCI Express Compiler Release Information

Item Description

Version 11.1

Release Date November 2011

Ordering Codes No ordering code is required

Product IDs There are no encrypted files for the Cyclone V Hard IP for PCI

Express. The Product ID and Vendor ID are not required

because this IP core does not require a license.

Vendor ID

Table 1–3. Device Family Support

Device Family Support

Cyclone V

Preliminary. The IP core is verified with preliminary timing

models. The IP core meets all functional requirements, but

is still undergoing characterization. It can be used in

production designs with caution.

Other device families

Refer to the following user guides for other device families:

■ IP Compiler for PCI Express User Guide

■ Stratix V Hard IP for PCI Express User Guide

■ Cyclone V Hard IP for PCI Express User Guide

Loading...

Loading...