Chapter 5: IP Core Interfaces 5–13

Avalon-ST TX Interface

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

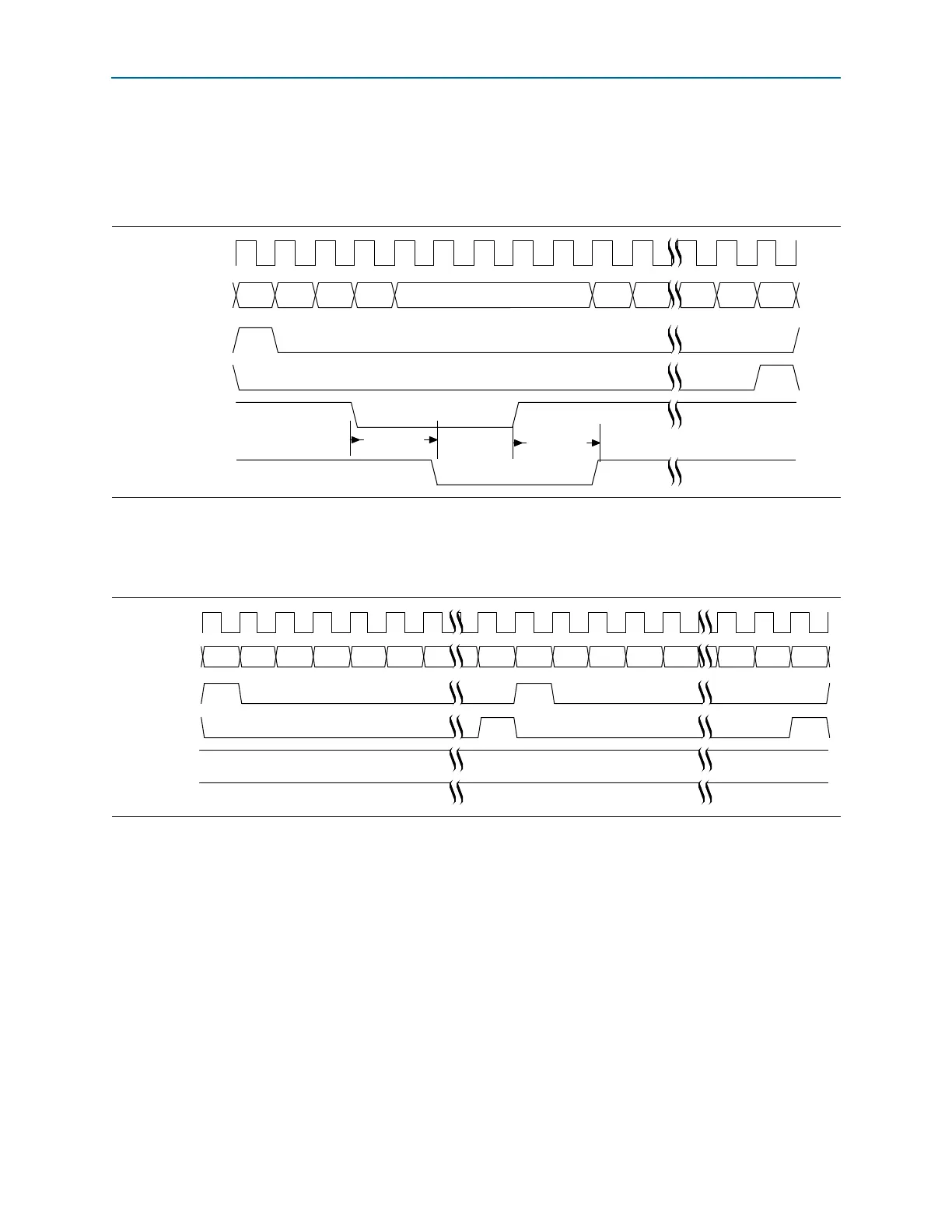

Figure 5–12 illustrates the timing of the TX interface when the Cyclone V Hard IP for

PCI Express IP core backpressures the Application Layer by deasserting

tx_st_ready

.

Because the

readyLatency

is two cycles, the Application Layer deasserts

tx_st_valid

after two cycles and holds

tx_st_data

until two cycles after

tx_st_ready

is asserted.

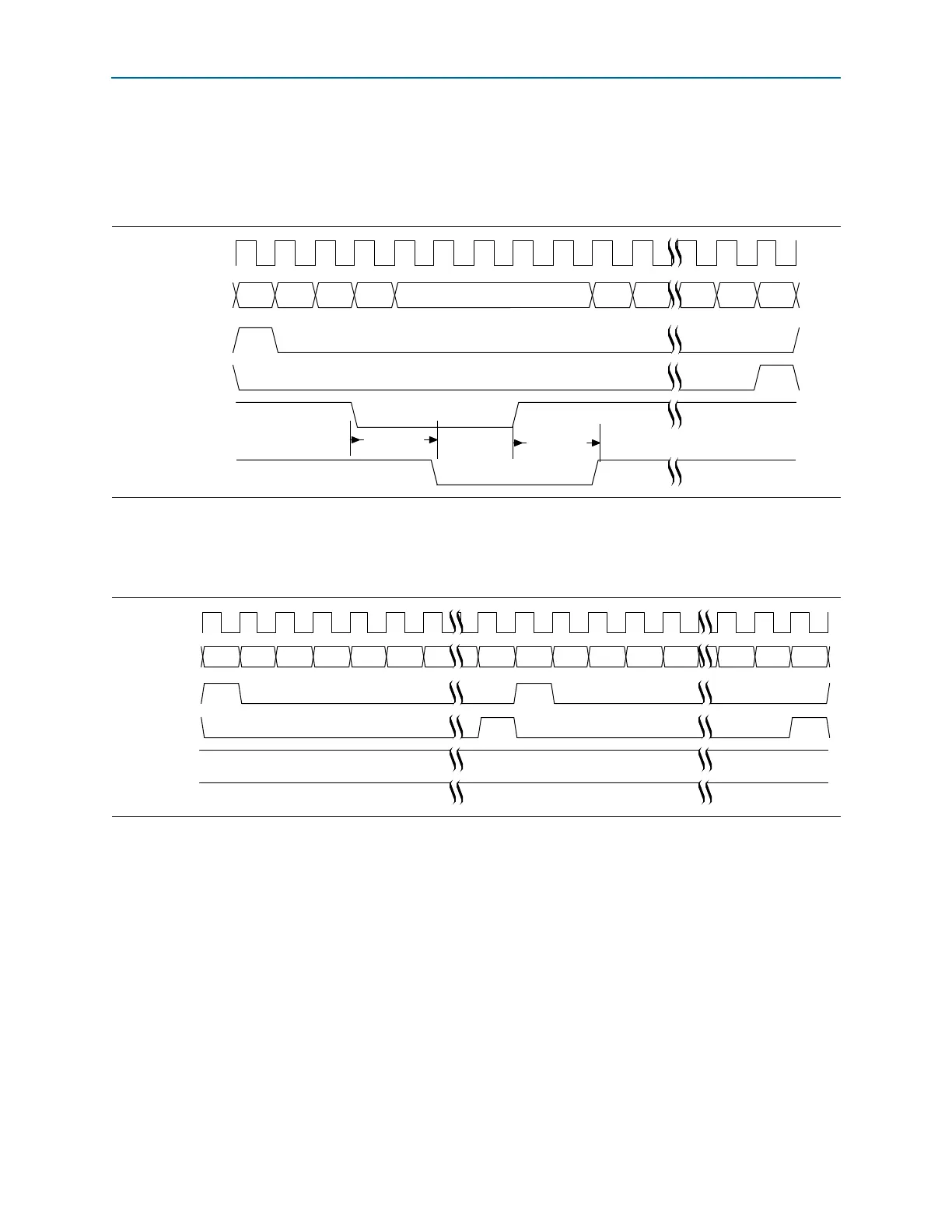

Figure 5–13 illustrates back-to-back transmission of 64-bit packets with no intervening

dead cycles between the assertion of

tx_st_eop

and

tx_st_sop

.

Root Port Mode Configuration Requests

If your Application Layer implements ECRC forwarding, it should not apply ECRC

forwarding to Configuration Type 0 packets that it issues on the Avalon-ST interface.

There should be no ECRC appended to the TLP, and the

TD

bit in the TLP header

should be set to 0. These packets are processed internally by the Hard IP block and

are not transmitted on the PCI Express link.

Figure 5–12. 64-Bit Transaction Layer Backpressures the Application Layer

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_data[63:0]

.. . . . . . . . . 00. . 00 ... BB... BB ... BBBB0306BBB0305A BB ... BB ... BB ... BB ... BB....

readyLatency

readyLatency

Figure 5–13. 64-Bit Back-to-Back Transmission on the TX Interface

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_data[63:0]

01 . 00 . BB . BB . BB . BB . B. . BB . 01 . 00 . CC . CC . CC . CC . CC . CC .

Loading...

Loading...