Chapter 5: IP Core Interfaces 5–5

Avalon-ST RX Interface

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

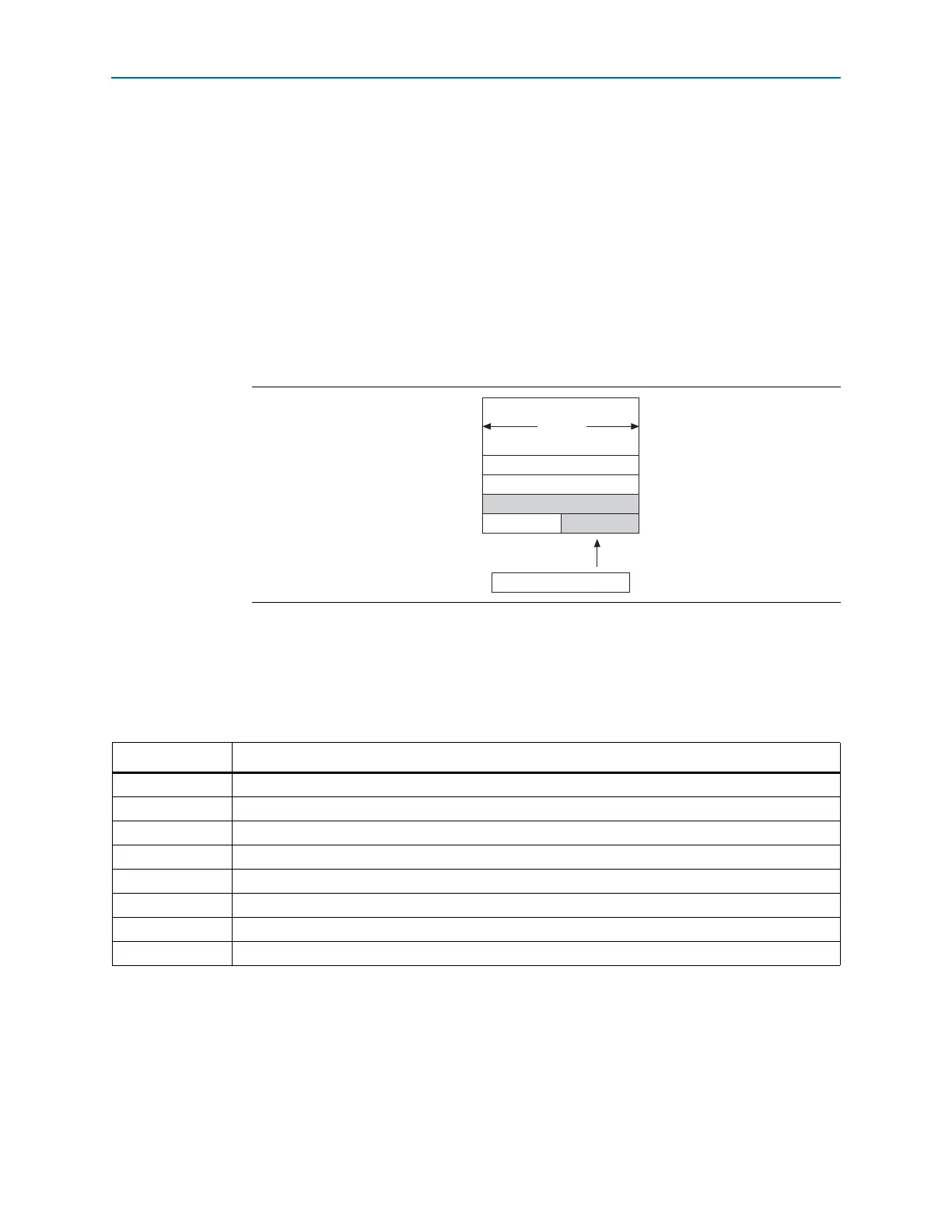

To facilitate the interface to 64-bit memories, the Cyclone V Hard IP for PCI Express

aligns data to the qword or 64 bits by default; consequently, if the header presents an

address that is not qword aligned, the Hard IP block shifts the data within the qword

to achieve the correct alignment. Figure 5–2 shows how an address that is not qword

aligned, 0x4, is stored in memory. The byte enables only qualify data that is being

written. This means that the byte enables are undefined for 0x0–0x3. This example

corresponds to Figure 5–3 on page 5–6. Qword alignment applies to all types of

request TLPs with data, including memory writes, configuration writes, and I/O

writes. The alignment of the request TLP depends on bit 2 of the request address. For

completion TLPs with data, alignment depends on bit 2 of the

lower

address

field.

This bit is always 0 (aligned to qword boundary) for completion with data TLPs that

are for configuration read or I/O read requests

.

f Refer to Appendix A, Transaction Layer Packet (TLP) Header Formats for the formats

of all TLPs.

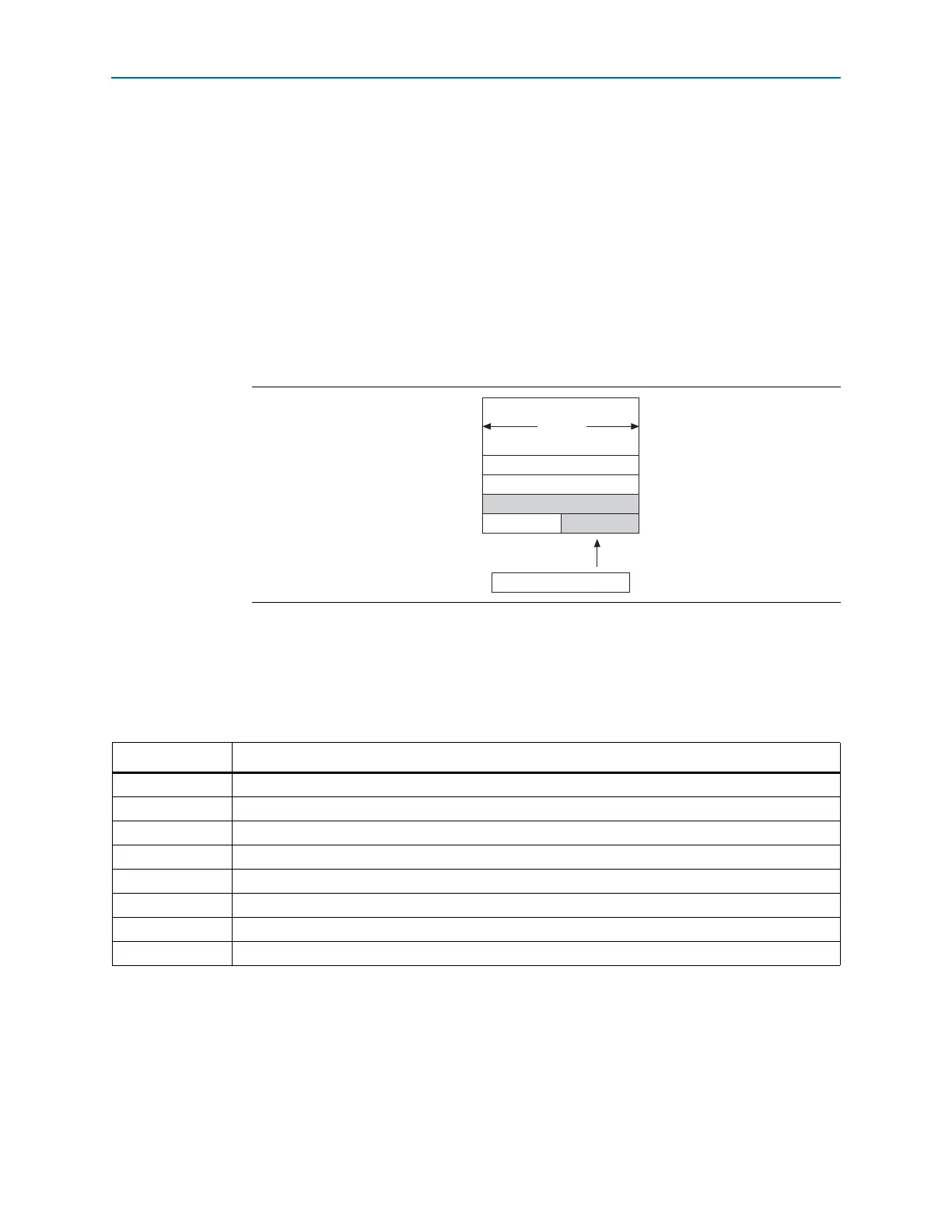

Table 5–3 shows the byte ordering for header and data packets.

Data Alignment and Timing for the 64-Bit Avalon-ST RX Interface

Figure 5–3 illustrates the mapping of Avalon-ST RX packets to PCI Express TLPs for a

three dword header with non-qword aligned addresses with a 64-bit bus. In this

example, the byte address is unaligned and ends with 0x4, causing the first data to

correspond to

rx_st_data[63:32]

.

Figure 5–2. Qword Alignment

.

.

.

0x0

0x8

0x10

0x18

Header Addr = 0x4

64 bits

PCB Memory

Valid Data

Valid Data

Table 5–3. Mapping Avalon-ST Packets to PCI Express TLPs

Packet TLP

Header0 pcie_hdr_byte0, pcie_hdr _byte1, pcie_hdr _byte2, pcie_hdr _byte3

Header1 pcie_hdr _byte4, pcie_hdr _byte5, pcie_hdr byte6, pcie_hdr _byte7

Header2 pcie_hdr _byte8, pcie_hdr _byte9, pcie_hdr _byte10, pcie_hdr _byte11

Header3 pcie_hdr _byte12, pcie_hdr _byte13, header_byte14, pcie_hdr _byte15

Data0 pcie_data_byte3, pcie_data_byte2, pcie_data_byte1, pcie_data_byte0

Data1 pcie_data_byte7, pcie_data_byte6, pcie_data_byte5, pcie_data_byte4

Data2 pcie_data_byte11, pcie_data_byte10, pcie_data_byte9, pcie_data_byte8

Data<n> pcie_data_byte<4n+3>, pcie_data_byte<4n+2>, pcie_data_byte<4n+1>, pcie_data_byte<n>

Loading...

Loading...