5–4 Chapter 5: IP Core Interfaces

Avalon-ST RX Interface

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

f For more information about the Avalon-ST protocol, refer to the Avalon Interface

Specifications.

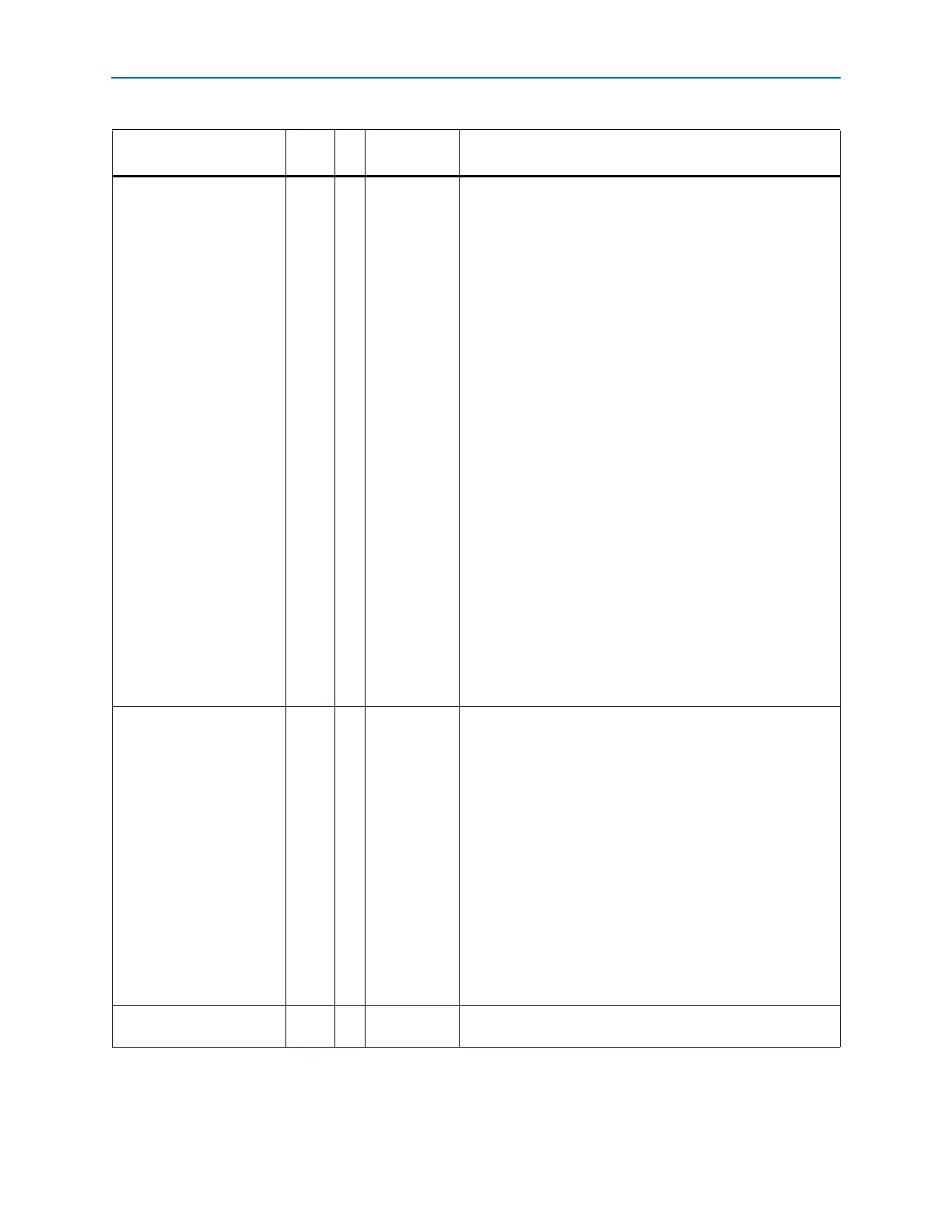

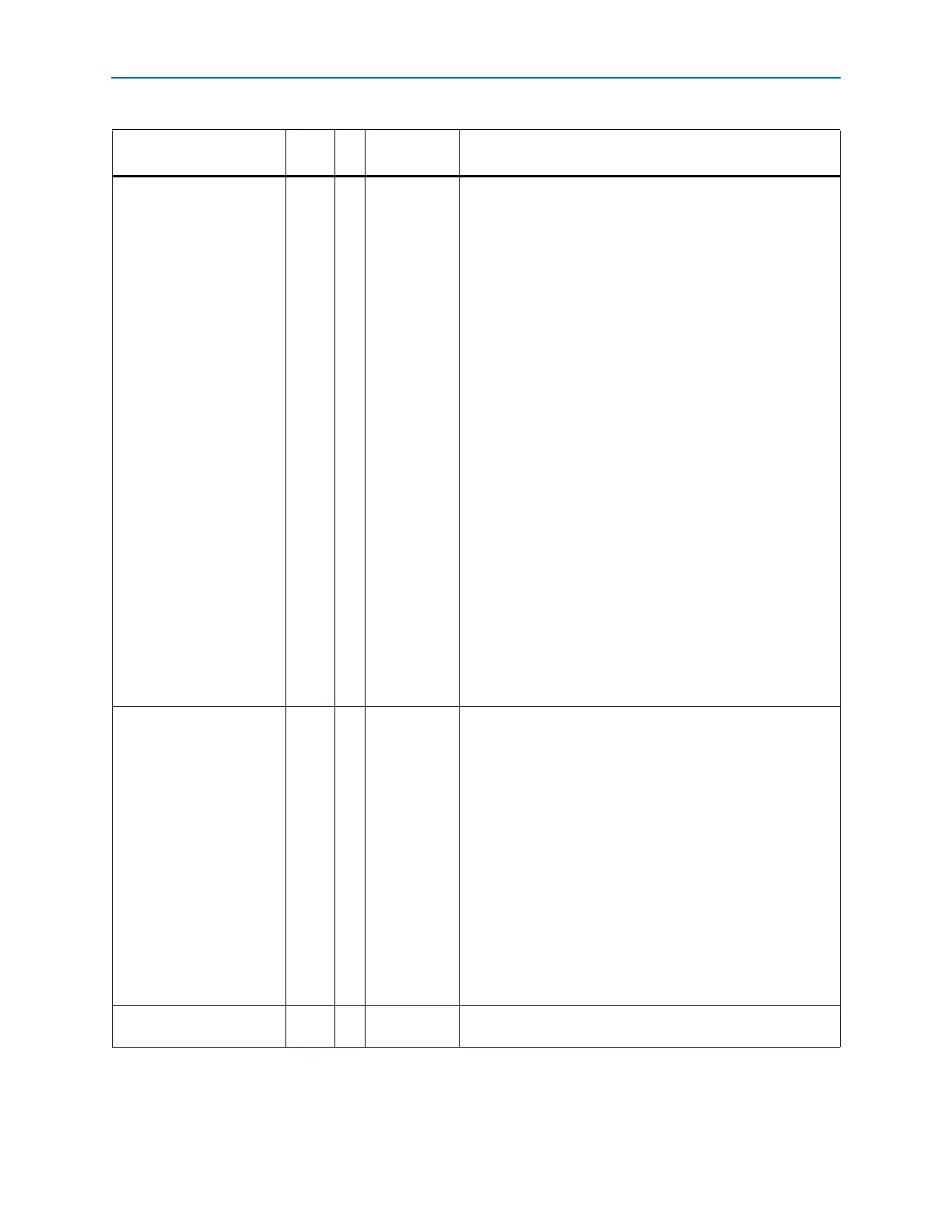

rx_st_bar

8O

component

specific

The decoded BAR bits for the TLP. Valid for

MRd

,

MWr

,

IOWR

, and

IORD

TLPs; ignored for the completion or message TLPs. Valid

during the cycle in which

rx_st_sop

is asserted. Figure 5–6

illustrates the timing of this signal for 64-bit data.

The following encodings are defined for Endpoints:

■ Bit 0: BAR 0

■ Bit 1: BAR 1

■ Bit 2: Bar 2

■ Bit 3: Bar 3

■ Bit 4: Bar 4

■ Bit 5: Bar 5

■ Bit 6: Expansion ROM

■ Bit 7: Reserved

The following encodings are defined for Root Ports:

■ Bit 0: BAR 0

■ Bit 1: BAR 1

■ Bit 2: Primary Bus number

■ Bit 3: Secondary Bus number

■ Bit 4: Secondary Bus number to Subordinate Bus number

window

■ Bit 5: I/O window

■ Bit 6: Non-Prefetchable window

■ Bit 7: Prefetchable window

rx_st_be

8O

component

specific

Byte enables corresponding to the

rx_st_data

. The byte

enable signals only apply to PCI Express TLP payload fields.

When using 64-bit Avalon-ST bus, the width of

rx_st_be

is 8

bits. This signal is optional. You can derive the same

information by decoding the

FBE

and

LBE

fields in the TLP

header. The byte enable bits correspond to data bytes as

follows:

rx_st_data[63:56]

=

rx_st_be[7]

rx_st_data[55:48]

=

rx_st_be[6]

rx_st_data[47:40]

=

rx_st_be[5]

rx_st_data[39:32]

=

rx_st_be[4]

rx_st_data[31:24]

=

rx_st_be[3]

rx_st_data[23:16]

=

rx_st_be[2]

rx_st_data[15:8]

=

rx_st_be[1]

rx_st_data[7:0]

=

rx_st_be[0]

This signal is deprecated.

rx_bar_dec_func_num

3O

component

specific

Specifies which function the

rx_st_bar

signal applies to.

Table 5–2. 64- or 128-Bit Avalon-ST RX Datapath (Part 2 of 2)

Signal Width Dir

Avalon-ST

Type

Description

Loading...

Loading...