November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

6. Register Descriptions

This section describes registers that you can access the PCI Express Configuration

Space. It includes the following sections:

■ Configuration Space Register Content

■ Correspondence between Configuration Space Registers and the PCIe Spec 2.1

Configuration Space Register Content

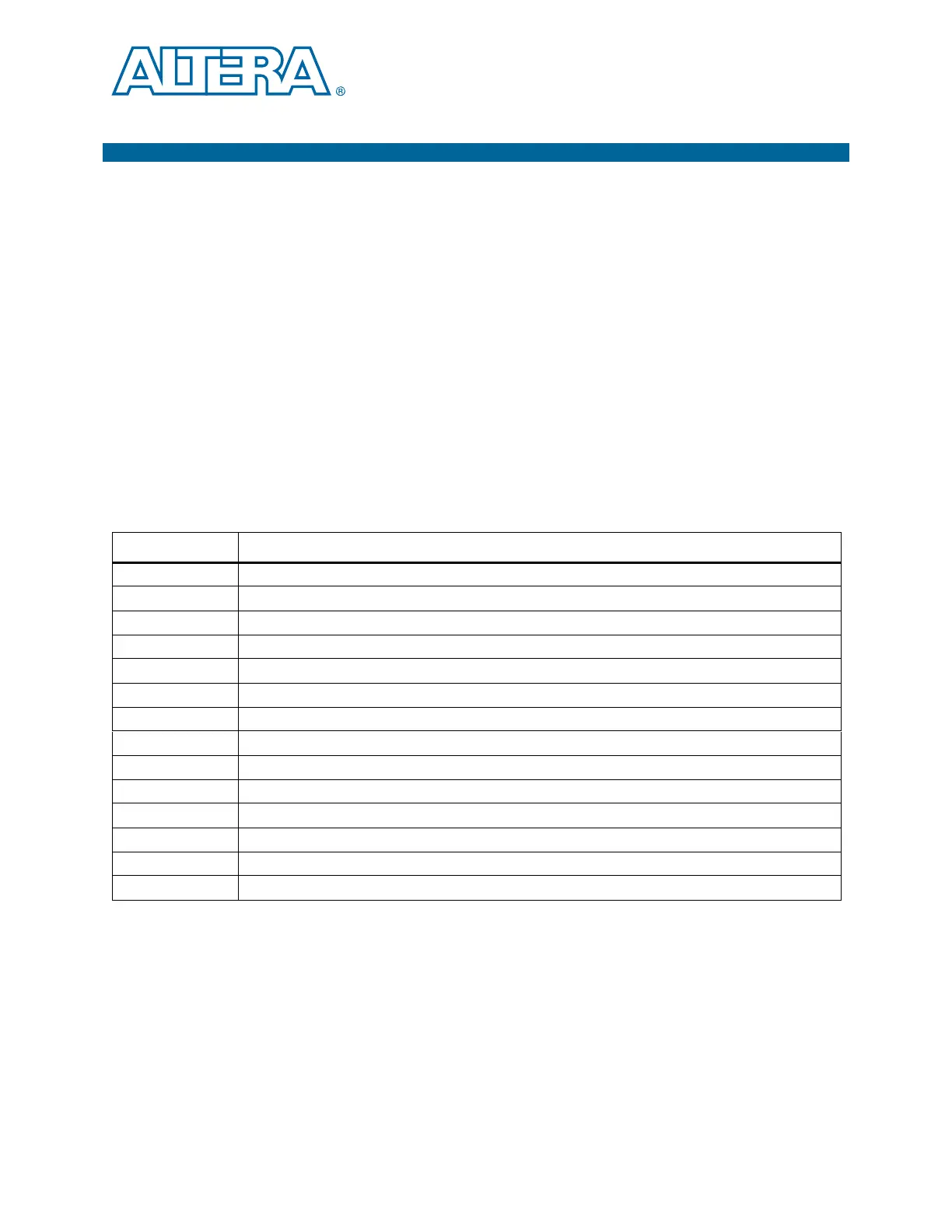

Table 6–1 shows the common Configuration Space header. The following tables

provide more details.

1 To facilitate finding additional information about these PCI Express registers, the

following tables provide the name of the corresponding section in the PCI Express Base

Specification Revision 2.1.

f For comprehensive information about these registers, refer to Chapter 7 of the PCI

Express Base Specification Revision 2.1.

Table 6–1. Common Configuration Space Header

Byte Offset Register Set

0x000:0x03C PCI Type 0 Configuration Space Header (Refer to Table 6–2 for details.)

0x000:0x03C PCI Type 1 Configuration Space Header (Refer to Table 6–3 for details.)

0x040:0x04C Reserved.

0x050:0x05C MSI Capability Structure, Version 1.0a and 1.1 (Refer to Table 6–4 for details.)

0x060:0x064 Reserved

0x068:0x070 MSI-X Capability Structure, Version 2.1 (Refer to Table 6–5 for details.)

0x070:0x074 Reserved

0x078:0x07C Power Management Capability Structure (Refer to Table 6–6 for details.)

0x080:0x0BC PCI Express Advanced Error Reporting Extended Capability Structure (Refer to Table 6–8 for details.)

0x0BD:0x0BF Reserved

0x0C0:0x0C4 Subsystem ID and Subsystem Vendor ID

0x0C8-0x7FC Reserved

0x800:0x834 Advanced error reporting (AER) (optional)

0x838:0xFFF Reserved

November 2011

1101

Loading...

Loading...