Chapter 5: IP Core Interfaces 5–27

LMI Signals

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

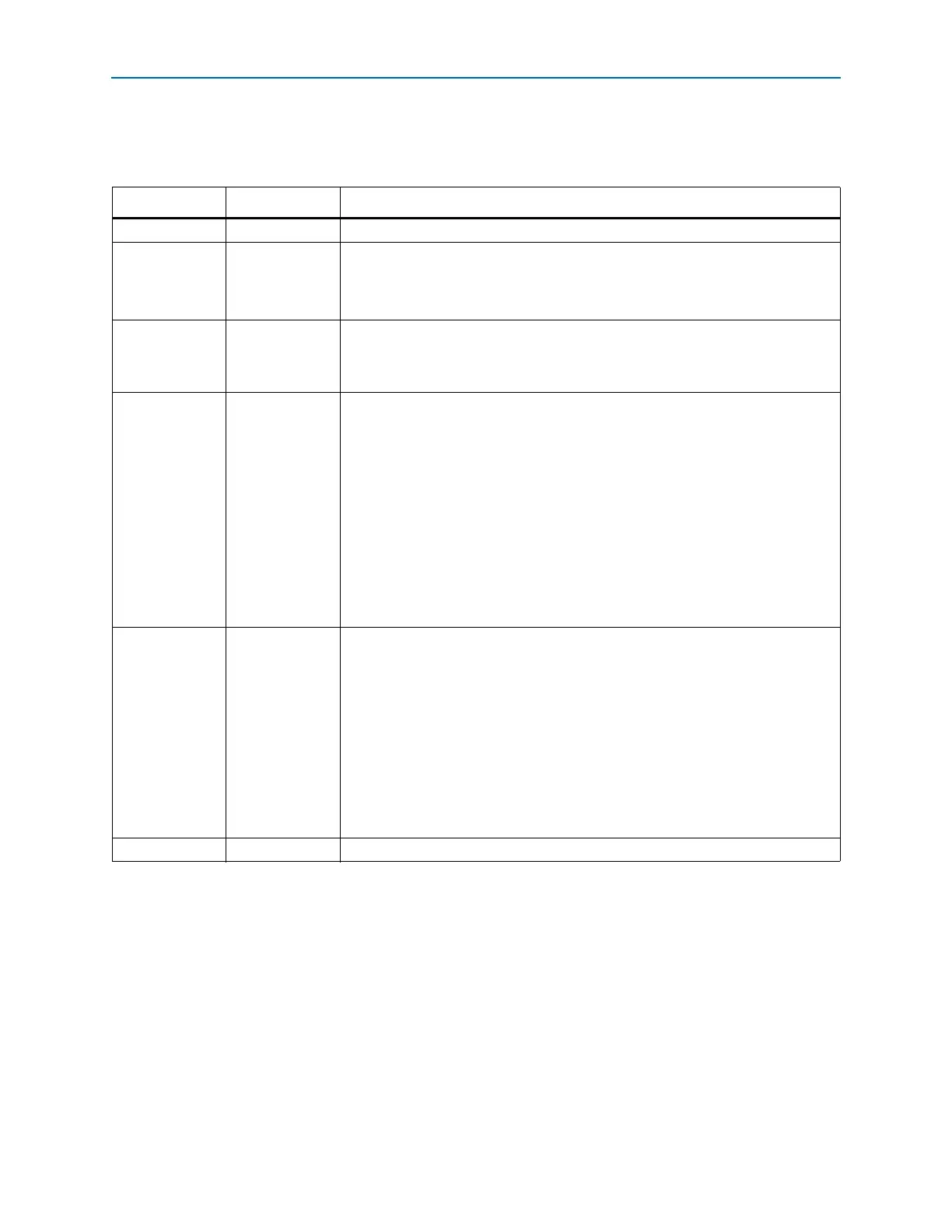

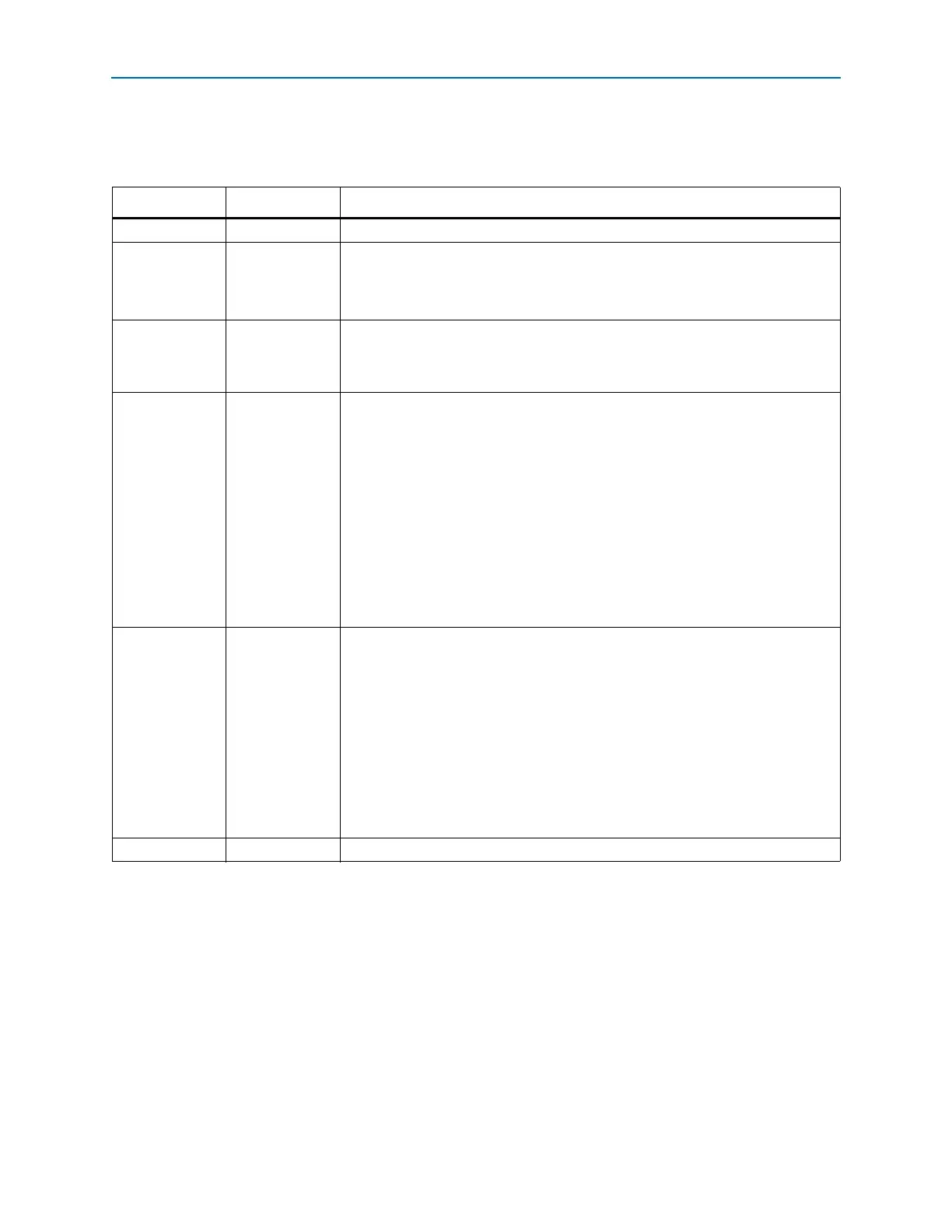

Table 5–15 describes the use of the various fields of the Configuration MSI Control

and Status Register.

LMI Signals

LMI interface is used to write log error descriptor information in the TLP header log

registers. The LMI access to other registers is intended for debugging, not normal

operation.

Table 5–15. Configuration MSI Control Status Register Field Descriptions

Bit(s) Field Description

[15:9]

reserved

—

[8]

mask

capability

Per vector masking capable. This bit is hardwired to 0 because the functions do not

support the optional MSI per vector masking using the

Mask_Bits

and

Pending_Bits

registers defined in the PCI Local Bus Specification, Rev. 3.0. Per

vector masking can be implemented using Application Layer registers.

[7]

64-bit

address

capability

64-bit address capable

■ 1: function capable of sending a 64-bit message address

■ 0: function not capable of sending a 64-bit message address

[6:4]

multiples

message

enable

Multiple message enable: This field indicates permitted values for MSI signals. For

example, if “100” is written to this field 16 MSI signals are allocated

■ 000: 1 MSI allocated

■ 001: 2 MSI allocated

■ 010: 4 MSI allocated

■ 011: 8 MSI allocated

■ 100: 16 MSI allocated

■ 101: 32 MSI allocated

■ 110: Reserved

■ 111: Reserved

[3:1]

multiple

message

capable

Multiple message capable: This field is read by system software to determine the

number of requested MSI messages.

■ 000: 1 MSI requested

■ 001: 2 MSI requested

■ 010: 4 MSI requested

■ 011: 8 MSI requested

■ 100: 16 MSI requested

■ 101: 32 MSI requested

■ 110: Reserved

[0]

MSI Enable

If set to 0, this component is not permitted to use MSI.

Loading...

Loading...