5–28 Chapter 5: IP Core Interfaces

LMI Signals

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

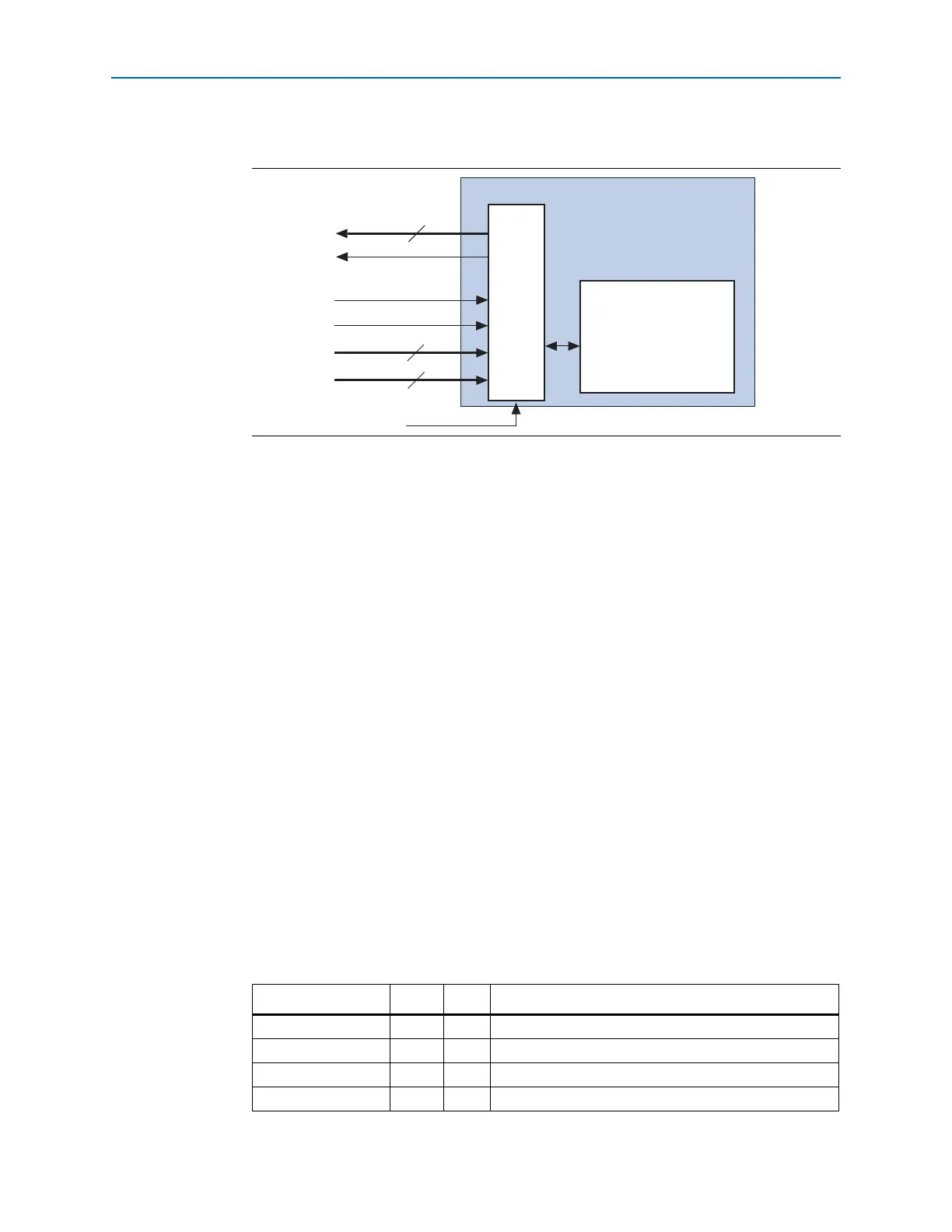

Figure 5–16 illustrates the LMI interface.

The LMI interface is synchronized to

pld_clk

and runs at frequencies up to 250 MHz.

The LMI address is the same as the Configuration Space address. The read and write

data are always 32 bits. The LMI interface provides the same access to Configuration

Space registers as Configuration TLP requests. Register bits have the same attributes,

(read only, read/write, and so on) for accesses from the LMI interface and from

Configuration TLP requests.

When a LMI write has a timing conflict with configuration TLP access, the

configuration TLP accesses have higher priority. LMI writes are held and executed

when configuration TLP accesses are no longer pending. An acknowledge signal is

sent back to the Application Layer when the execution is complete.

All LMI reads are also held and executed when no configuration TLP requests are

pending. The LMI interface supports two operations: local read and local write. The

timing for these operations complies with the Avalon-MM protocol described in the

Avalon Interface Specifications. LMI reads can be issued at any time to obtain the

contents of any Configuration Space register. LMI write operations are not

recommended for use during normal operation. The Configuration Space registers are

written by requests received from the PCI Express link and there may be unintended

consequences of conflicting updates from the link and the LMI interface. LMI Write

operations are provided for AER header logging, and debugging purposes only.

c In Root Port mode, do not access the Configuration Space using TLPs and the LMI bus

simultaneously.

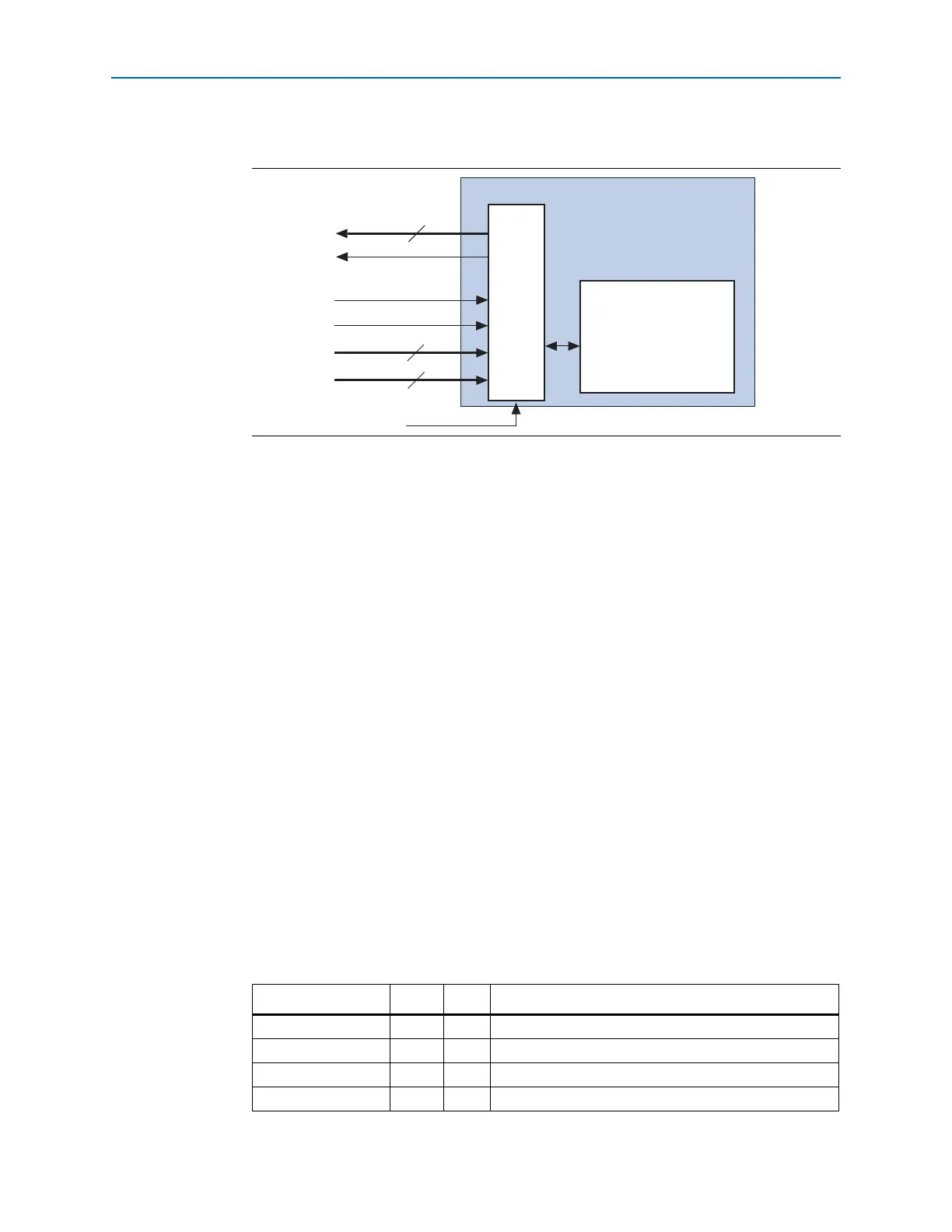

Table 5–16 describes the signals that comprise the LMI interface.

Figure 5–16. Local Management Interface

Configuration Space

128 32-bit registers

(4 KBytes)

LMI

32

lmi_dout

lmi_ack

12

lmi_addr

32

lmi_din

lmi_rden

lmi_wren

pld_clk

Hard IP for

PCI Express

Table 5–16. LMI Interface (Part 1 of 2)

Signal Width Dir Description

lmi_dout

32 O Data outputs

lmi_rden

1 I Read enable input

lmi_wren

1 I Write enable input

lmi_ack

1 O Write execution done/read data valid

Loading...

Loading...