5–26 Chapter 5: IP Core Interfaces

Transaction Layer Configuration Space Signals

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

Table 5–15 shows the layout of the Configuration MSI Control Status register.

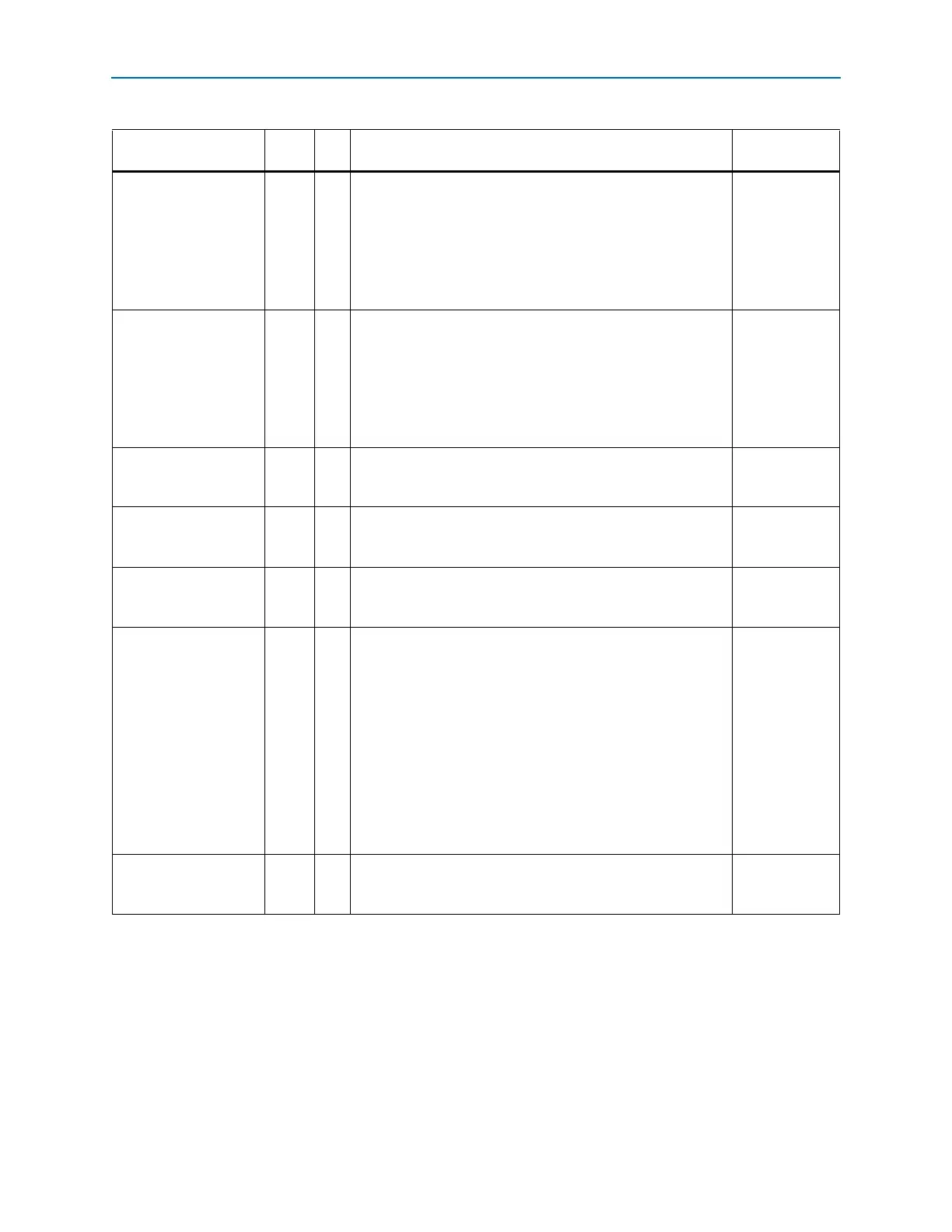

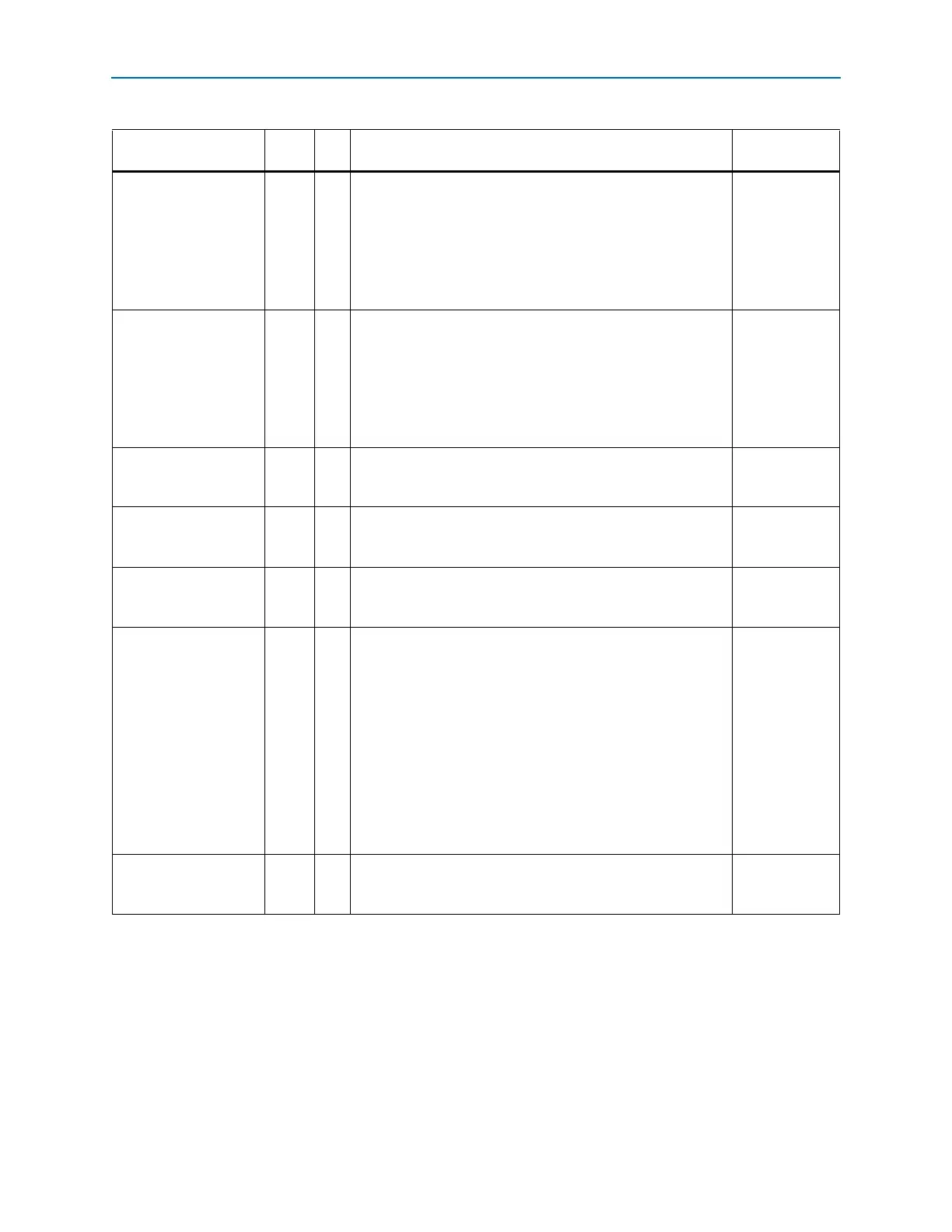

cfg_pr_bas

44 O

The upper 44 bits of the prefetchable base registers of the

Type1 Configuration Space. This register is only available in

Root Port mode.

Table 6–3 on

page 6–2

0x024 and

Table 3–7 on

page 3–8

Prefetchable

memory

cfg_pr_lim

44 O

The upper 44 bits of the prefetchable limit registers of the Type1

Configuration Space. Available in Root Port mode.

Table 6–3 on

page 6–2

0x024 and

Table 3–7 on

page 3–8

Prefetchable

memory

cfg_pmcsr

32 O

cfg_pmcsr[31:16]

is Power Management Control and

cfg_pmcsr[15:0]

is the Power Management Status register.

Table 6–6 on

page 6–4

0x07C

cfg_msixcsr

16 O MSI-X message control.

Table 6–5 on

page 6–3

0x068

cfg_msicsr

16 O

MSI message control. Refer to Table 5–15 for the fields of this

register.

Table 6–4 on

page 6–3

0x050

cfg_tcvcmap

24 O

Configuration traffic class (TC)/virtual channel (VC) mapping.

The Application Layer uses this signal to generate a TLP

mapped to the appropriate channel based on the traffic class of

the packet.

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0).

cfg_tcvcmap[5:3]

: Mapping for TC1.

cfg_tcvcmap[8:6]

: Mapping for TC2.

cfg_tcvcmap[11:9]

: Mapping for TC3.

cfg_tcvcmap[14:12]

: Mapping for TC4.

cfg_tcvcmap[17:15]

: Mapping for TC5.

cfg_tcvcmap[20:18]

: Mapping for TC6.

cfg_tcvcmap[23:21]

: Mapping for TC7.

—

cfg_busdev

13 O Bus/Device Number captured by or programmed in the Hard IP.

Table A–5 on

page A–2

0x08

Table 5–14. Configuration Space Register Descriptions (Part 3 of 3)

Register

Width Dir Description

Register

Reference

Loading...

Loading...