Chapter 2: Getting Started 2–11

Qsys Design Flow

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

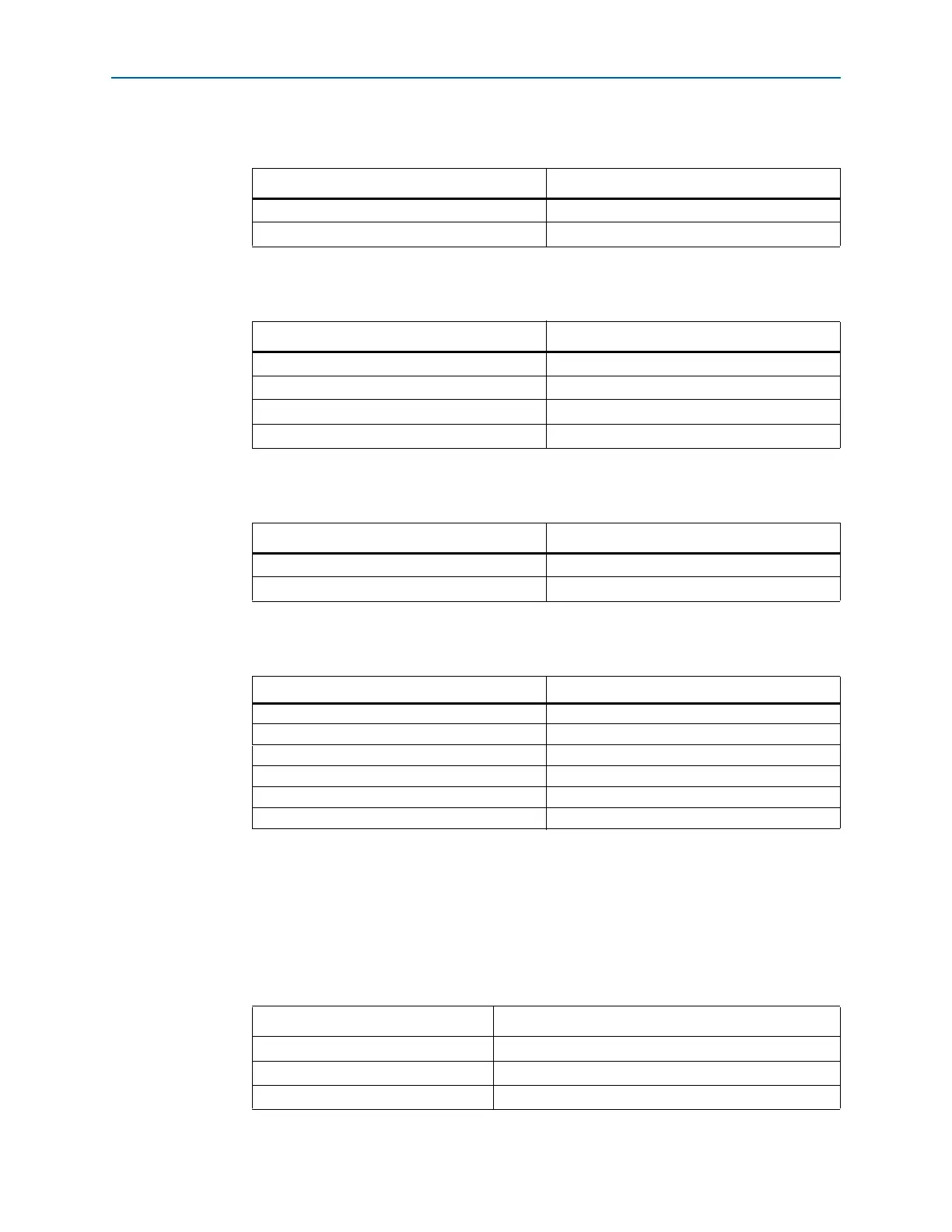

4. Specify the Link settings listed in Table 2–11.

5. Specify the Slot settings listed in Table 2–12.

6. Specify the Power Management settings listed in.Table 2–13.

7. Specify the BAR settings for Func0 listed in Table 2–14.

8. You can leave Func0 BAR3 through Func0 BAR5 and the Func0 Expansion ROM

Disabled.

9. Under the Base and Limit Registers heading, disable both the Input/Output and

Prefetchable memory options. (These options are for Root Ports.)

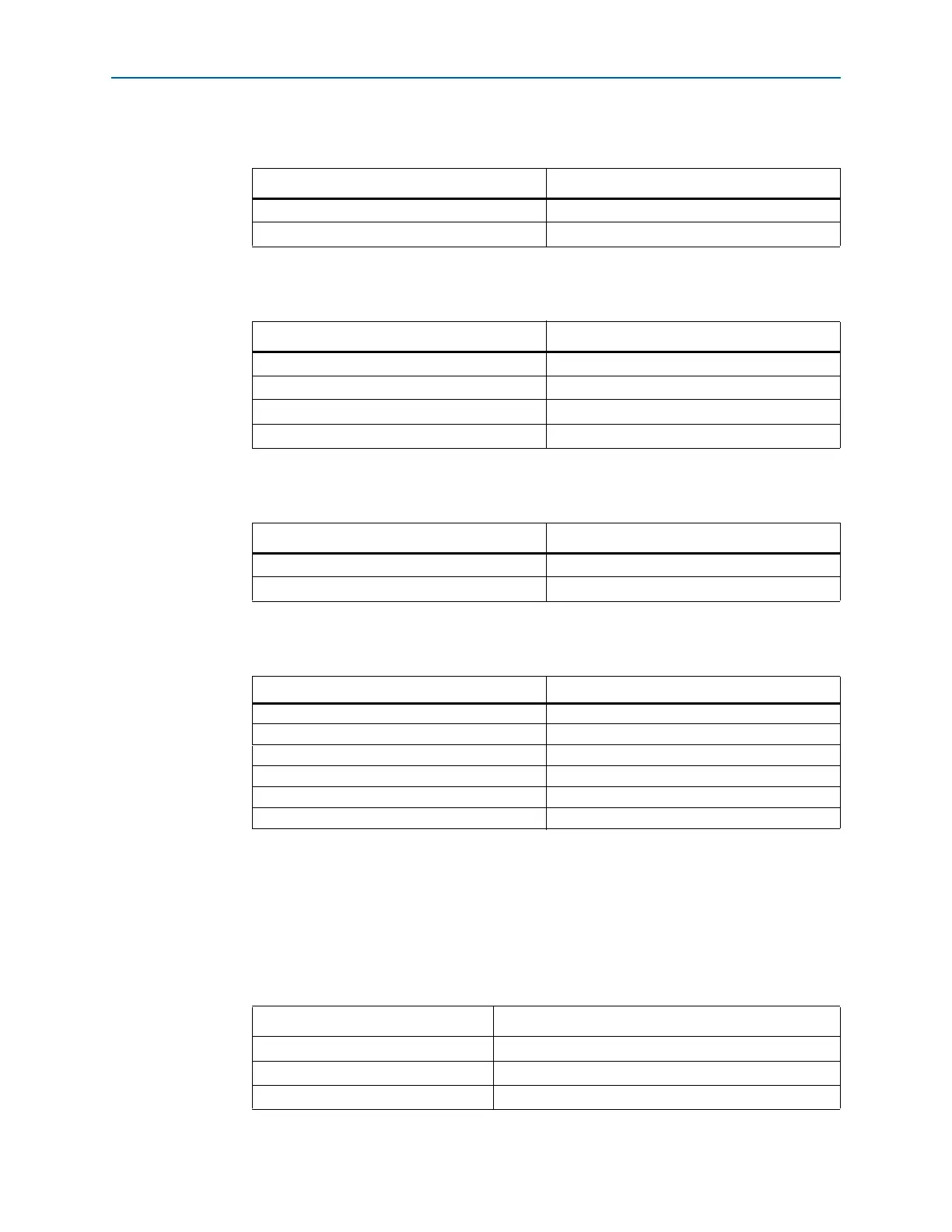

10. Specify the Device ID Registers for Func0 listed in Table 2–15.

Table 2–11. Link Tab

Parameter Value

Link port number 1

Slot clock configuration Enabled

Table 2–12. Link Tab

Parameter Value

Use slot register Leave this option off.

Data link layer active reporting 0

Surprise down reporting 0

Slot clock configuration 0

Table 2–13. Power Management Parameters

Parameter Value

Endpoint L0s acceptable exit latency Maximum of 64 ns

Endpoint L1 acceptable latency Maximum of 1 µs

Table 2–14. Base Address Registers for Func0

Parameter Value

BAR0 Type 64-bit prefetchable memory

BAR0 Size 256 MBytes - 28 bits

BAR1 Type Disabled

BAR1 Size N/A

BAR2 Type 32-bit non-prefetchable memory

BAR2 Size 1 KByte - 10 bits

Table 2–15. Device Identification Registers for Func0 (Part 1 of 2)

Register Name Value

Vendor ID

0x00000000

Device ID

0x00000001

Revision ID

0x00000001

Loading...

Loading...