Chapter 5: IP Core Interfaces 5–35

Physical Layer Interface Signals

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

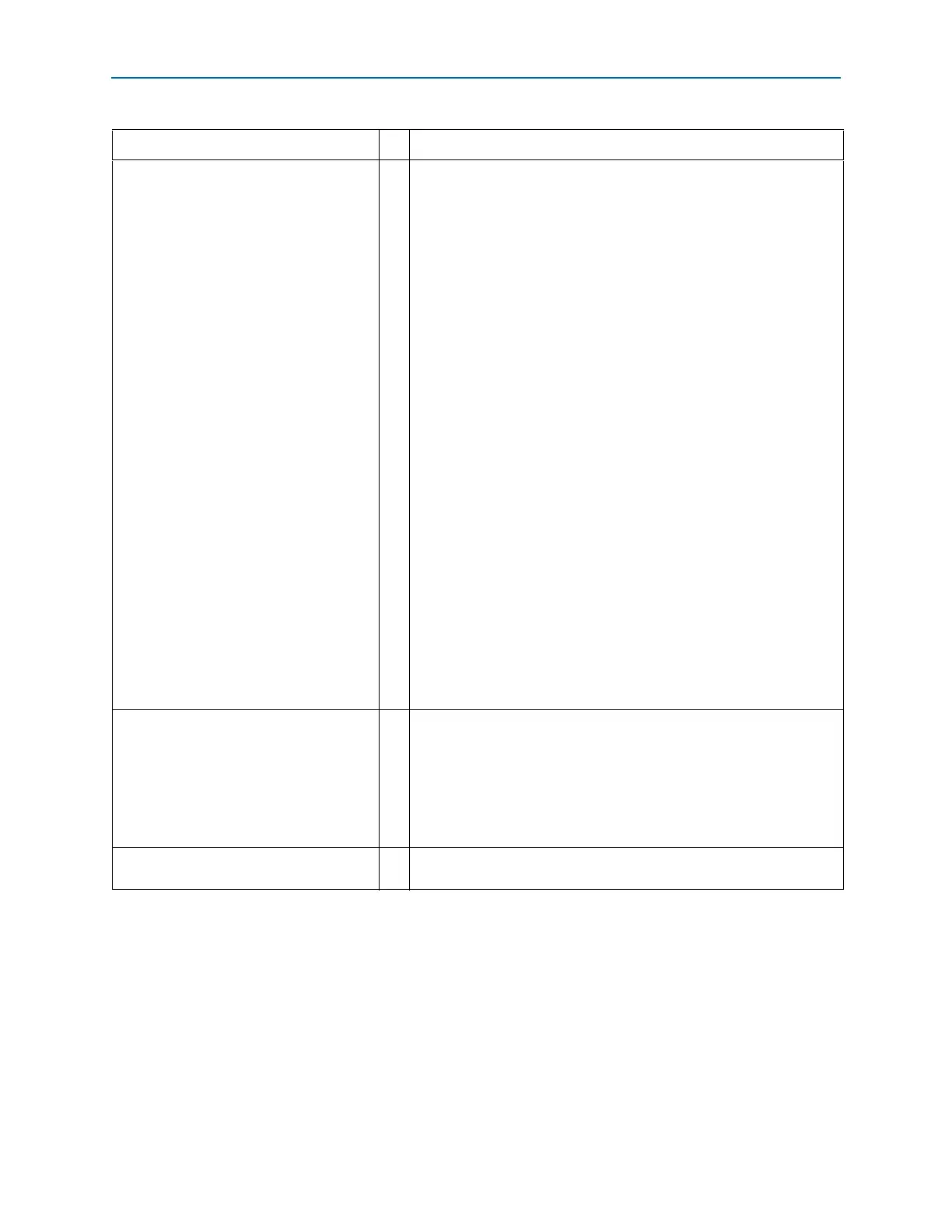

ltssmstate0[4:0]

LTSSM state: The LTSSM state machine encoding defines the following

states:

■ 00000: detect.quiet

■ 00001: detect.active

■ 00010: polling.active

■ 00011: polling.compliance

■ 00100: polling.configuration

■ 00101: polling.speed

■ 00110: config.linkwidthstart

■ 00111: config.linkaccept

■ 01000: config.lanenumaccept

■ 01001: config.lanenumwait

■ 01010: config.complete

■ 01011: config.idle

■ 01100: recovery.rcvlock

■ 01101: recovery.rcvconfig

■ 01110: recovery.idle

■ 01111: L0

■ 10000: disable

■ 10001: loopback.entry

■ 10010: loopback.active

■ 10011: loopback.exit

■ 10100: hot.reset

■ 10101: LOs

■ 11001: L2.transmit.wake

■ 11010: speed.recovery

O

sim_pipe_rate

O

Specifies the lane rate. The 2-bit encodings have the following

meanings:

■ 2’b00–reserved

■ 2’b01: Gen1 rate (2.5 Gbps)

■ 2’b10: Gen2 rate (5.0 Gbps)

■ 2’b11–Gen3 rate (8.0 Gbps)

sim_pipe_pclk_in

I

This clock is used for PIPE simulation only, and is derived from the

refclk

. It is the PIPE interface clock used for PIPE mode simulation.

Notes to Table 5–22:

(1) Signals that include lane number 0 also exist for lanes 1-7.

(2) These signals are for simulation only. For Quartus II software compilation, these pipe signals can be left floating.

Table 5–22. PIPE Interface Signals (Part 3 of 3)

Signal I/O Description

Loading...

Loading...