Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

Revision 1.8 23

Intel Order Number: E14960-009

When SPI is selected by the Boot BIOS Destination Strap and a SPI Device is detected by the

Intel

®

ICH9, LPC-based BIOS Flash is disabled. The boot destination strap is sampled by the

ICH9 at pins GNT# and SPI_CS1# on the rising edge of the PWROK input. Alternately, the

ICH9 supports soft straps when operating in Descriptor Mode. The ICH9 reads the soft strap

data out of the SPI device prior to de-assertion of reset to the Manageability Engine and the

Host system.

GNT# and SPI_CS1# are both pulled-up with soft resistors internal to the Intel

®

ICH9. The

default BIOS flash without external straps is the FWH. For manufacturing or debugging support,

the BIOS cycles may also be directed to the PCI bridge via the same external flash.

Configurations other than the default are selected using 2.2K pull-up or pull-down resistors.

The server board supports the boot BIOS Destination Selection as defined in Table 8.

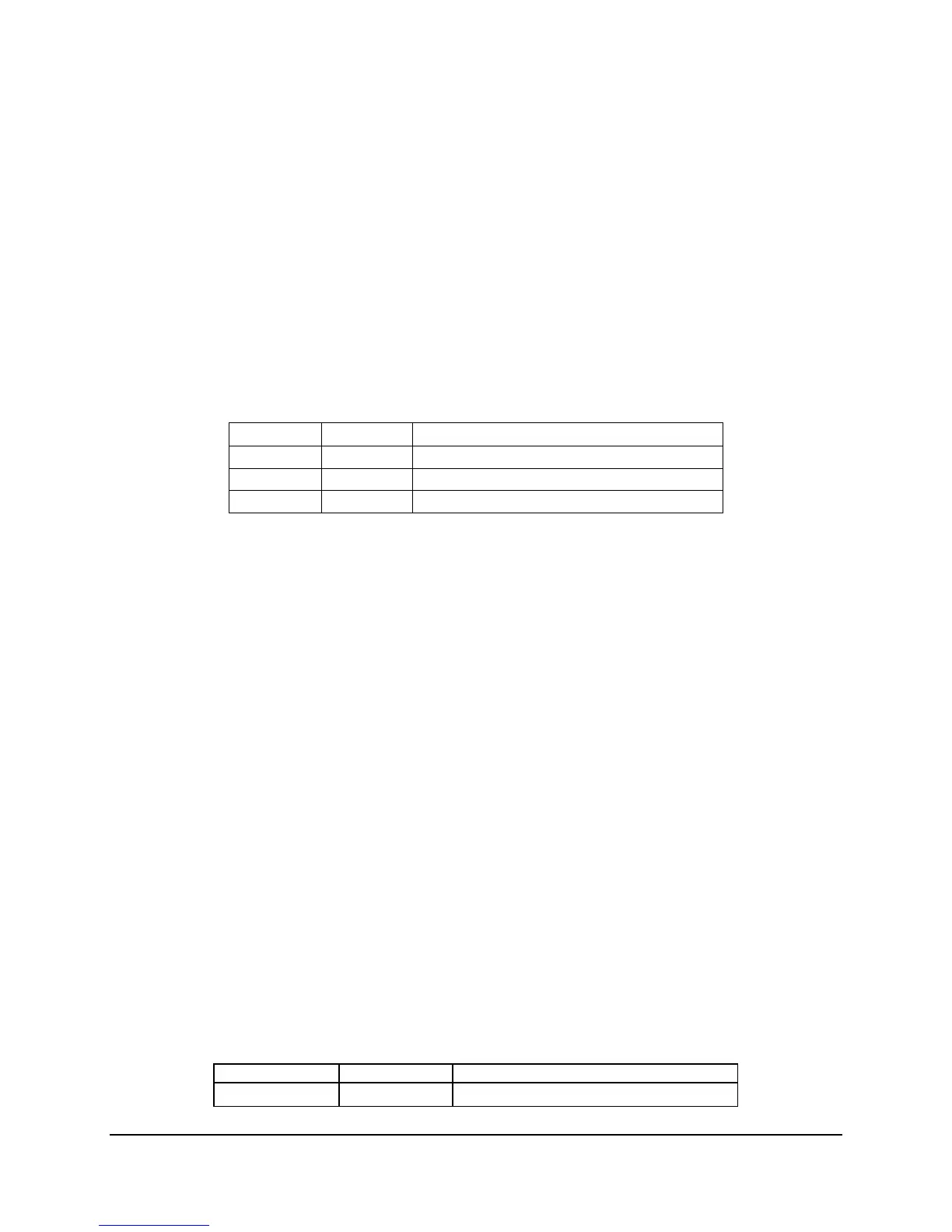

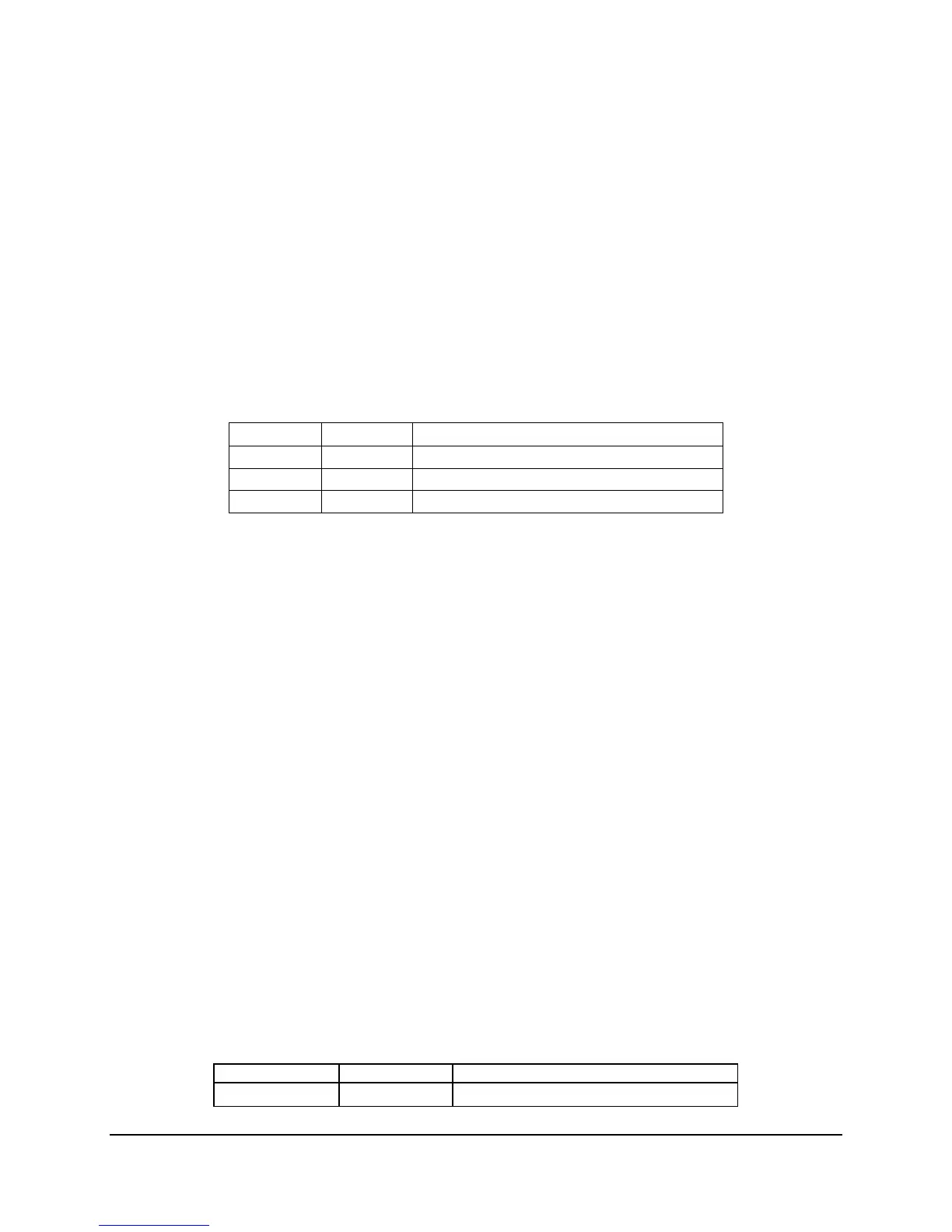

Table 8. Boot BIOS Destination Selection

GNT# SPI_CS1# ROUTING

0 1 Flash Cycles Routed to SPI (Default)

1 0 Flash Cycles Routed to PCI (Test only)

1 1 Flash Cycles Routed to LPC (Test only)

The SPI flash meets the following requirements:

Erase size capability of 4 Kbyte or 64 Kbyte

SPI device meets the command set per Table 9

For streamlined software development, command and opcode C7h (for Full Chip Erase) is

recommended.

Supports JEDEC ID OP Code 9FH.

Supports multiple writes to a page without requiring a preceding command (minimum

512 writes).

Ignores the upper address bit. For example, an address of FFFFFFFFh simply aliases to

the top of the flash memory.

Supports SPI Compatibility Mode 0.

Receipt of an unsupported command causes a completed cycle without impact to the

flash content.

Minimum density of 16 Mb (BIOS + Gbe).

To disable write protection, power up in an unlocked state or use the write status

register.

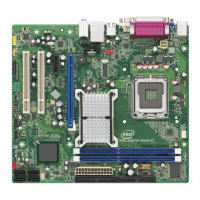

Table 9. SPI Required Command Codes

Commands Opcode Notes

Write Status 01h

If the command is supported, the opcode

Loading...

Loading...