Intel® Server Boards S3200SH/S3210SH TPS Error Reporting and Handling

Revision 1.8 77

Intel Order Number: E14960-009

5. Error Reporting and Handling

This chapter defines the following error handling features:

Error Handling and Logging

Error Messages and Beep Codes

5.1 Error Handling and Logging

This section defines how errors are handled by the system BIOS. In addition, this section

describes error-logging techniques and defines error beep codes.

5.1.1 Error Sources and Types

One of the major requirements of server management is to correctly and consistently handle

system errors. System errors you can enable and disable individually or as a group are

categorized as follows:

PCI bus

Memory single- and multi-bit errors

Errors detected during POST, logged as POST errors

The event list follows:

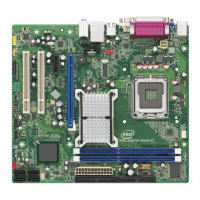

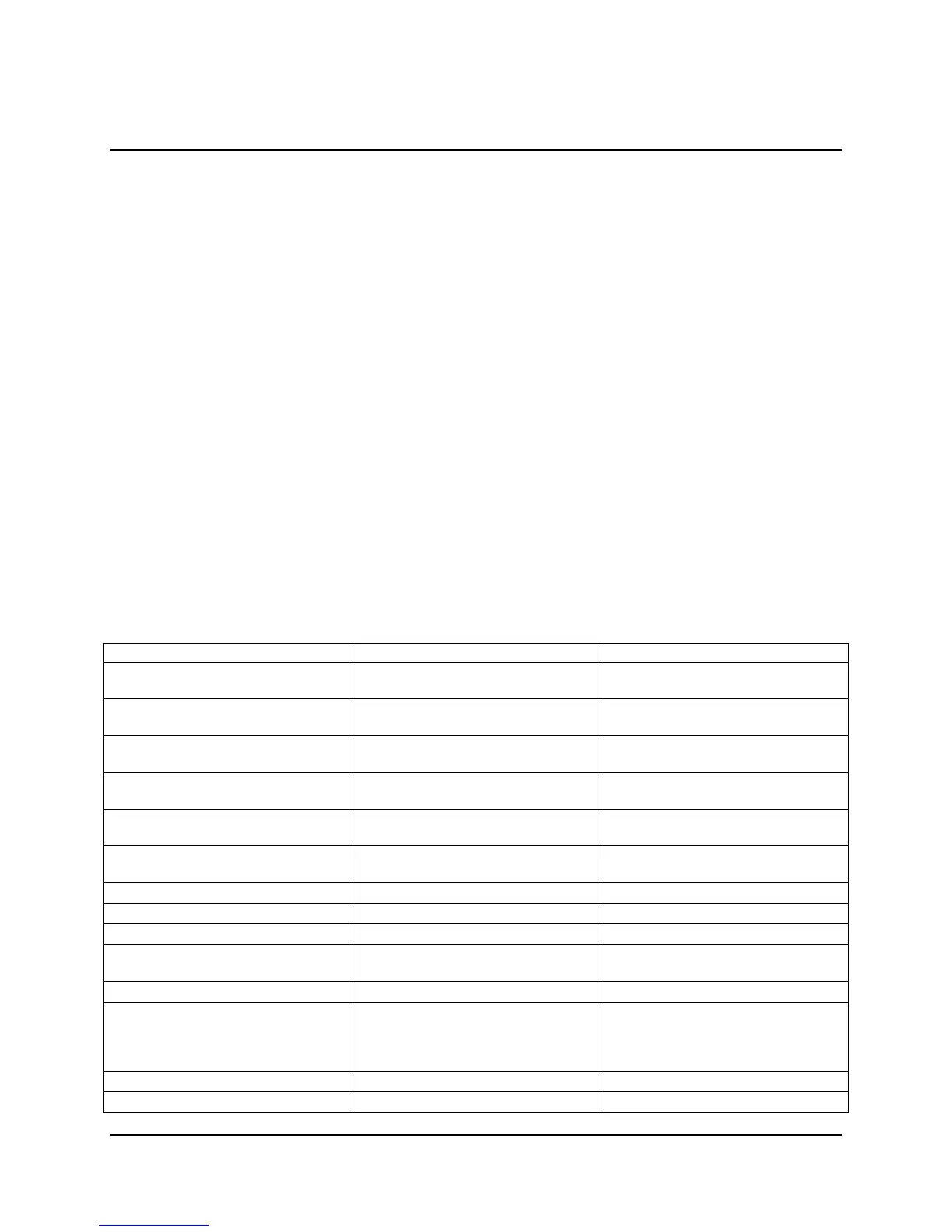

Table 41. Event List

Event Name Description When Error Is Caught

Processor thermal trip of last boot Processor thermal trip happened on

last boot.

POST

Memory channel A Multi-bit ECC

error

Multi-bit ECC error happened on

DIMM channel A.

POST / Runtime

Memory channel A Single-bit ECC

error

Single-bit ECC error happened on

DIMM channel A.

POST / Runtime

Memory channel B Multi-bit ECC

error

Multi-bit ECC error happened on

DIMM channel B.

POST / Runtime

Memory channel B Single-bit ECC

error

Single-bit ECC error happened on

DIMM channel B.

POST / Runtime

CMOS battery failure CMOS battery failure or CMOS clear

jumper is set to clear CMOS.

POST

CMOS checksum error CMOS data crushed POST

CMOS time not set CMOS time is not set POST

Keyboard not found PS/2 KB is not found during POST POST

Memory size decrease Memory size is decreased compared

with last boot

POST

Chassis intrusion detected Chassis is open POST

Bad SPD tolerance Some fields of the DIMM SPD may

not be supported, but could be

tolerant by the Memory Reference

Code.

POST

PCI PERR error PERR error happens on PCI bus POST / Runtime

PCI SERR error SERR error happens on PCI bus POST / Runtime

Loading...

Loading...