Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

28 Revision 1.8

Intel Order Number: E14960-009

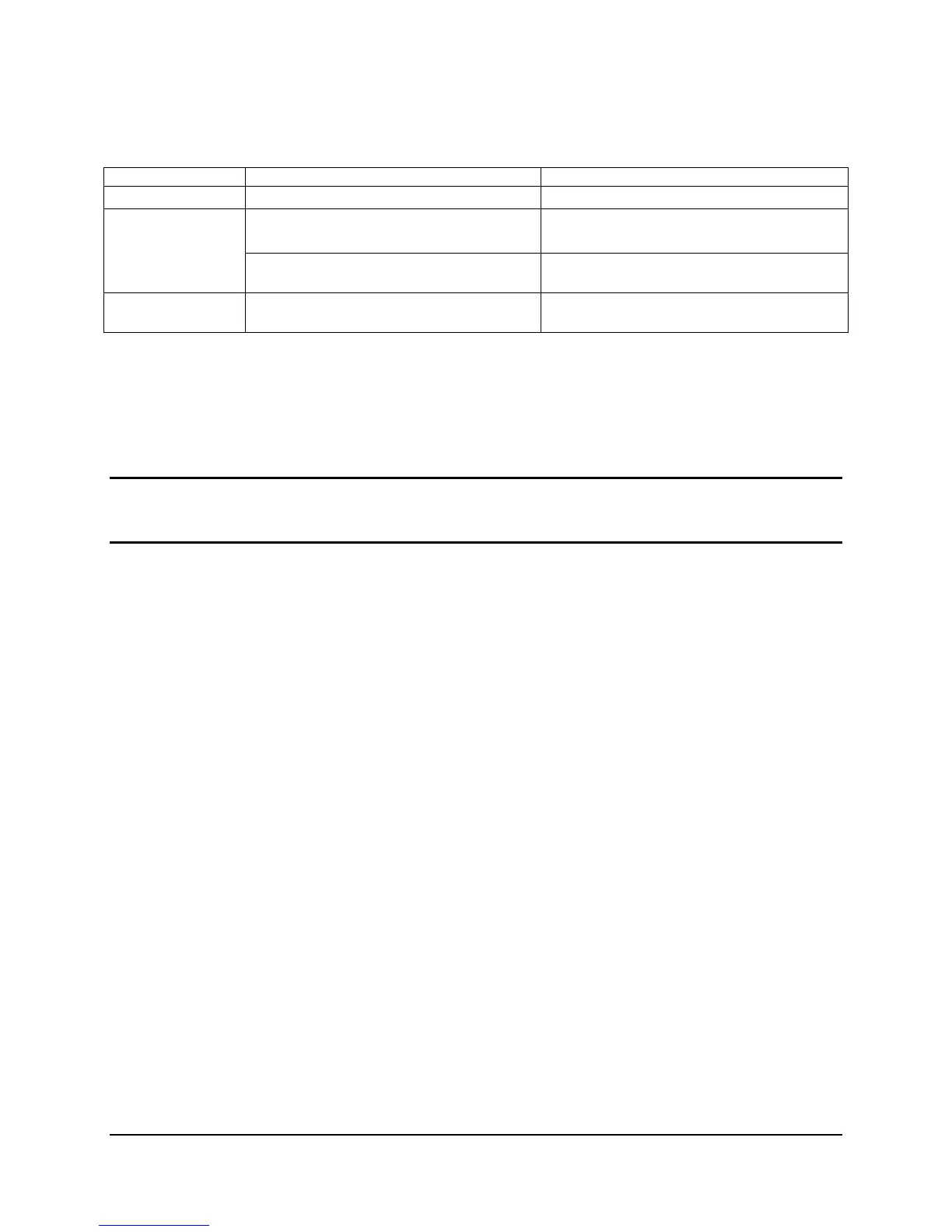

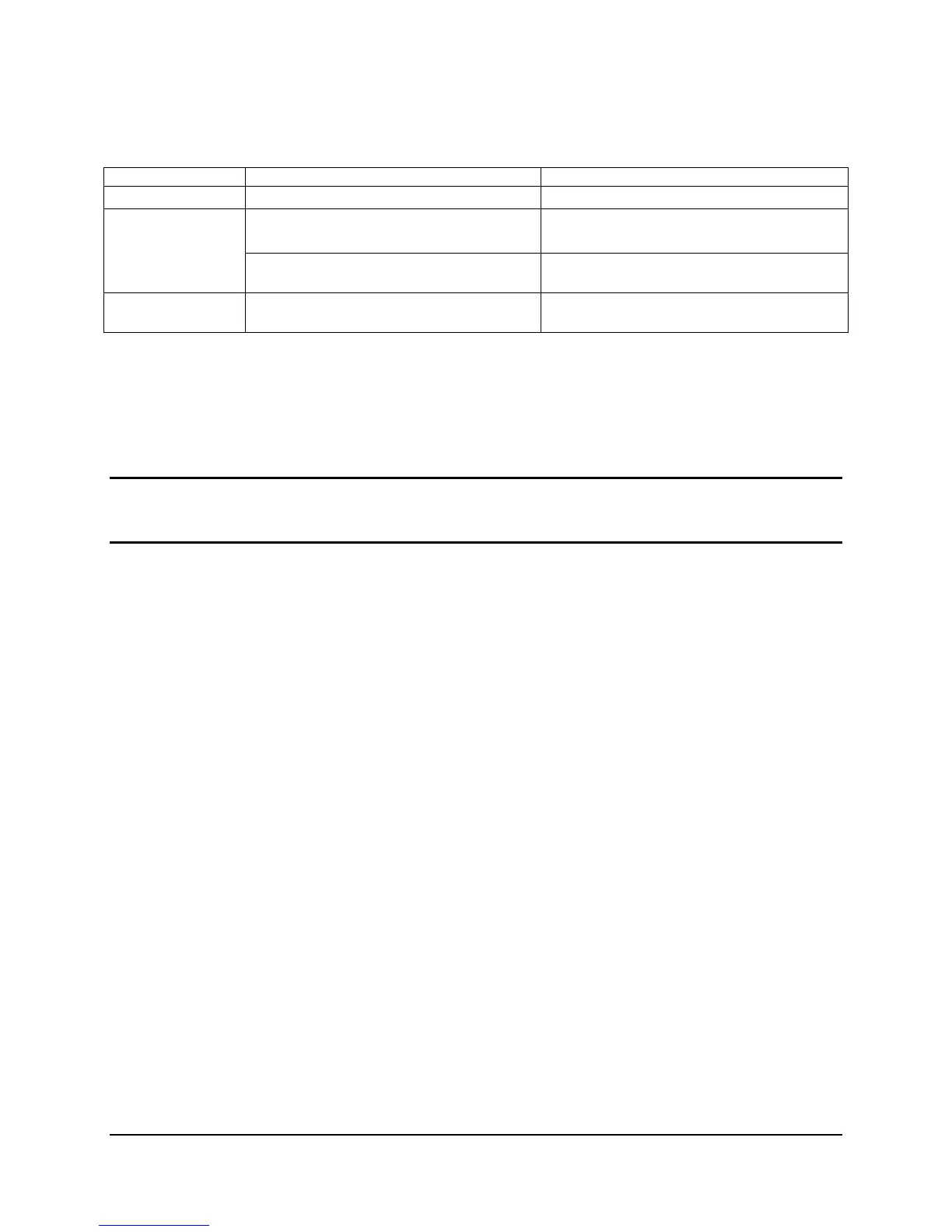

Table 11. Characteristics of Dual/Single Channel Configuration with or without Dynamic Mode

Throughput Level Configuration Characteristics

Highest Dual channel with dynamic paging mode All DIMMs matched

Dual channel without dynamic paging mode DIMMs matched from Channel A to Channel B

DIMMs not matched within channels

Single channel with dynamic paging mode Single DIMM or DIMMs matched within a

channel

Lowest Single channel without dynamic paging

mode

DIMMs not matched

3.3.2 Memory DIMM Support

The board supports unbuffered (not registered) DDR2 667/800 ECC or non-ECC DIMMs

operating at 667/800 MT/s.

Note: Only DIMMs tested and qualified by Intel or a designated memory test vendor are

supported on this board. All DIMMs are supported by design, but only fully qualified DIMMs are

supported on the board.

The minimum supported DIMM size is 512 MB. Therefore, the minimum main memory

configuration is 1 x 512 MB or 512 MB. The largest size DIMM supported is 2 GB and as such,

the maximum main memory configuration is 8 GB implemented by 4 x 2 GB DIMMs.

Unbuffered DDR2 667/800 compliant, ECC x8 and Non-ECC x8 or x16 memory DIMMs

are supported.

ECC single-bit errors (SBE) can be detected and corrected. Multiple-bit errors (MBE)

can only be detected.

The maximum memory capacity is 8 GB via four 2 GB DIMM modules.

The minimum memory capacity is 512 MB via a single 512 MB DIMM module.

3.4 I/O Sub-System

3.4.1 PCI Subsystem

The primary I/O buses for the server board are five independent PCI bus segments providing

PCI, PCI Express*, and PCI-X resources (LX board SKU only). The PCI buses comply with the

PCI Local Bus Specification, Rev 2.3.

PCI segments A, B, C, and D are directed through the Intel

®

ICH9R. PCI segment E is

independently configured to PXH-V which is through the Intel

®

ICH9R by PCI Express* x4

interface. PCI Segment F is directed through the MCH by PCI Express* x8 interface. Table 12

lists the characteristics of the three PCI bus segments.

Loading...

Loading...