Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

Revision 1.8 31

Intel Order Number: E14960-009

3.4.2.2 APIC Interrupt Routing

For APIC mode, the server board interrupt architecture incorporates three Intel

®

I/O APIC

devices to manage and broadcast interrupts to local APICs in each processor. The Intel

®

I/O

APICs monitor each interrupt on each PCI device including PCI slots in addition to the ISA

compatibility interrupts IRQ (0-15).

When an interrupt occurs, a message corresponding to the interrupt is sent across a three-wire

serial interface to the local APICs. The APIC bus minimizes interrupt latency time for

compatibility interrupt sources. The I/O APICs can also supply greater than 16 interrupt levels to

the processor(s). This APIC bus consists of an APIC clock and two bi-directional data lines.

3.4.2.3 Legacy Interrupt Sources

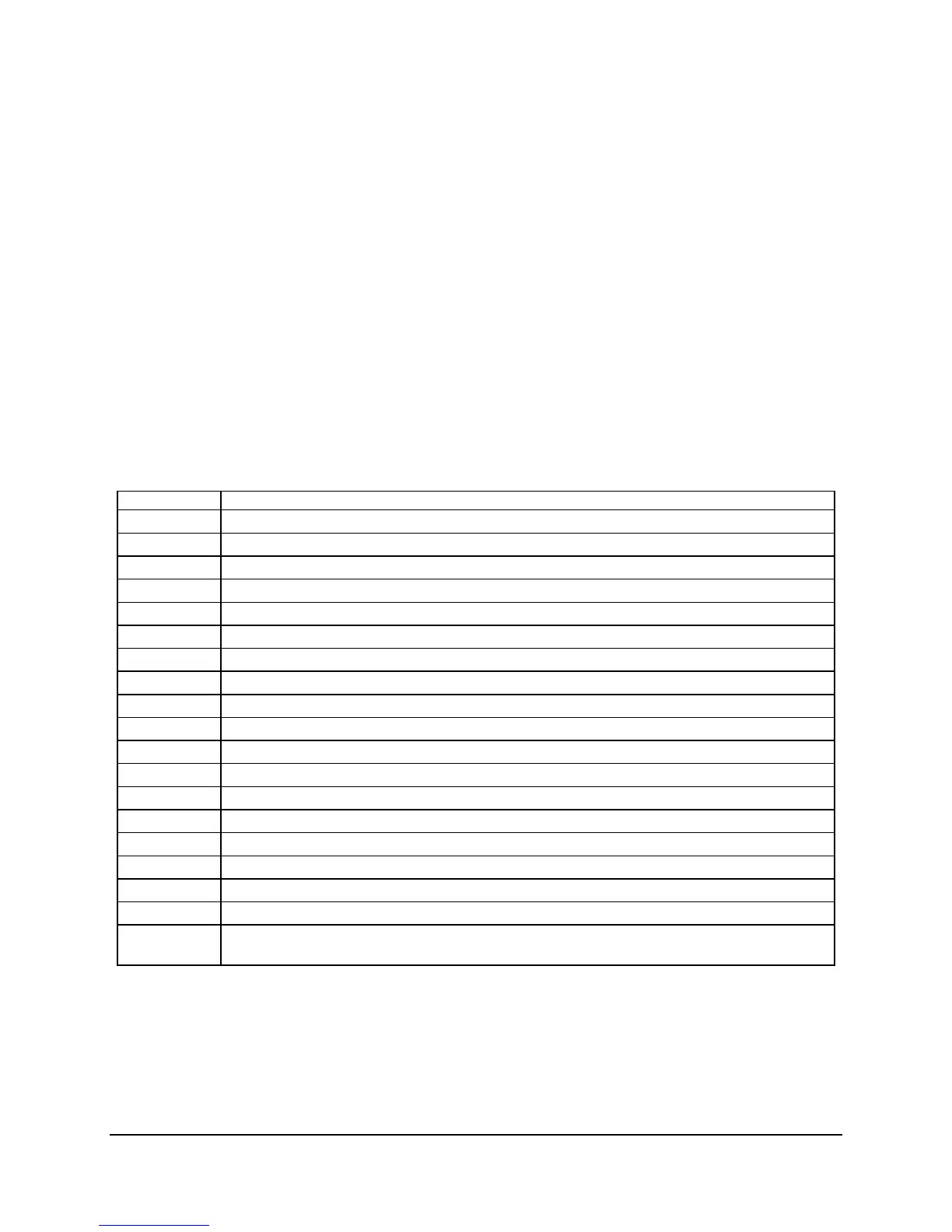

Table 16 recommends the logical interrupt mapping of interrupt sources on the board. The

actual interrupt map is defined using configuration registers in the Intel

®

ICH9R.

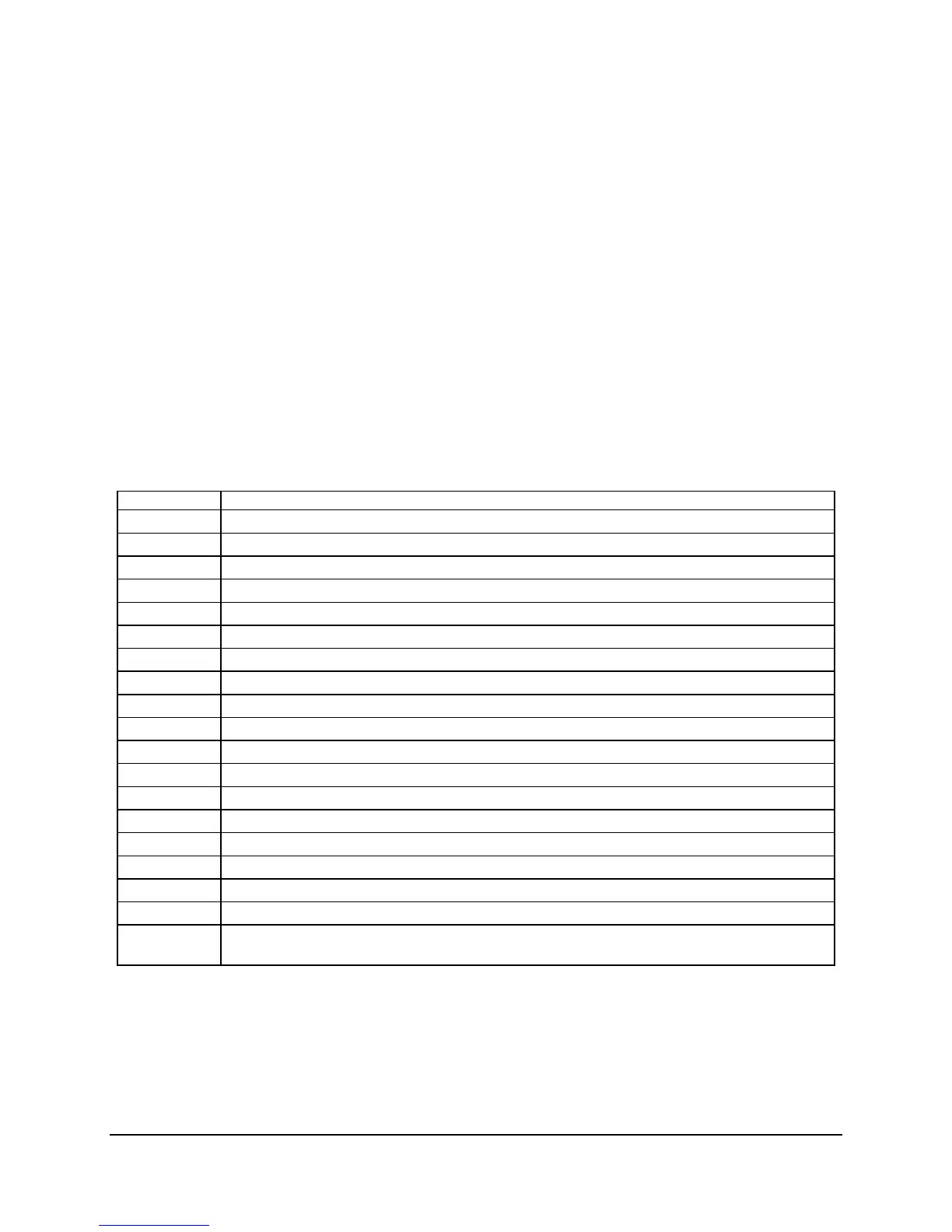

Table 16. Interrupt Definitions

ISA Interrupt Description

INTR Processor interrupt.

NMI NMI to processor.

IRQ0 System timer

IRQ1 Keyboard interrupt.

IRQ2 Slave PIC

IRQ3 Serial port 1 interrupt from Super I/O* device, user-configurable.

IRQ4 Serial port 1 interrupt from Super I/O* device, user-configurable.

IRQ5

IRQ6 Floppy disk.

IRQ7 Generic

IRQ8_L Active low RTC interrupt.

IRQ9 SCI*

IRQ10 Generic

IRQ11 Generic

IRQ12 Mouse interrupt.

IRQ13 Floaty processor.

IRQ14 Compatibility IDE interrupt from primary channel IDE devices 0 and 1

IRQ15 Secondary IDE Cable

SMI* System Management Interrupt: General purpose indicator sourced by the Intel

®

ICH9R to the

processor

3.4.2.4 Serialized IRQ Support

The server board supports a serialized interrupt delivery mechanism. Serialized Interrupt

Requests (SERIRQ) consist of a start frame, a minimum of 17 IRQ / data channels, and a stop

frame. Any slave device in the quiet mode may initiate the start frame. While in the continuous

mode, the start frame is initiated by the host controller.

Loading...

Loading...