Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

Revision 1.8 37

Intel Order Number: E14960-009

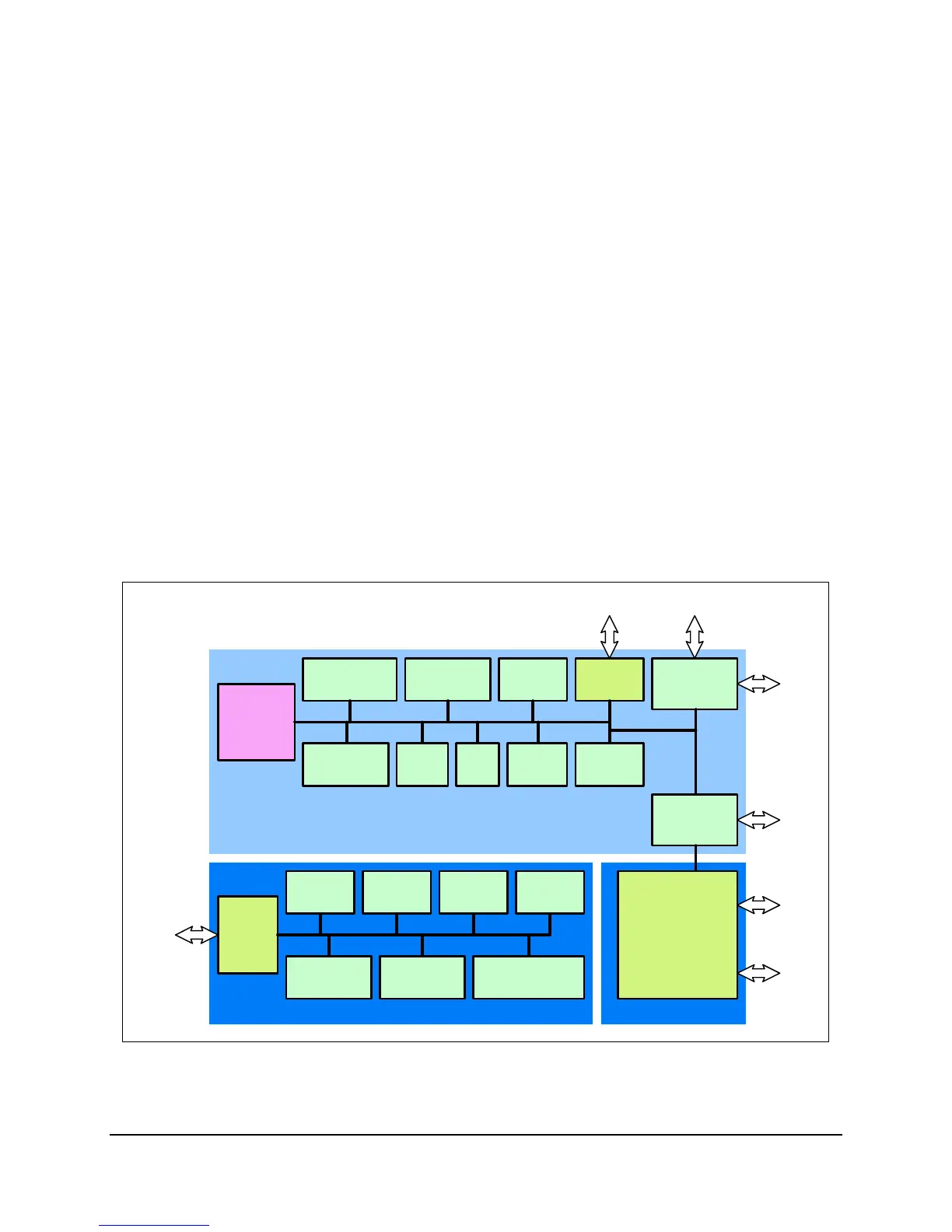

Eight Fan Tach Inputs

Four Pulse Width Modulators (PWM)

Chassis Intrusion Logic with battery backed general purpose register

LED support with programmable blink rate control

Programmable IO Port snooping, which can be used to snoop on Port 80h

Unique Chip ID for each part, burned at the time of production testing

Hardware 32-bit Random Number generator

JTAG Master interface

On-Chip Test Infrastructure for testing BMC firmware

Graphics Controller Subsystem

Integrated Matrix Graphics Core

2D Hardware Graphics Acceleration

DDR2 memory interface supports up to 128 Mbytes of memory

Supports all display resolutions up to 1600 x 1200 16 bpp @ 75 Hz

High speed Integrated 24-bit RAMDAC

Single lane PCI Express* host interface

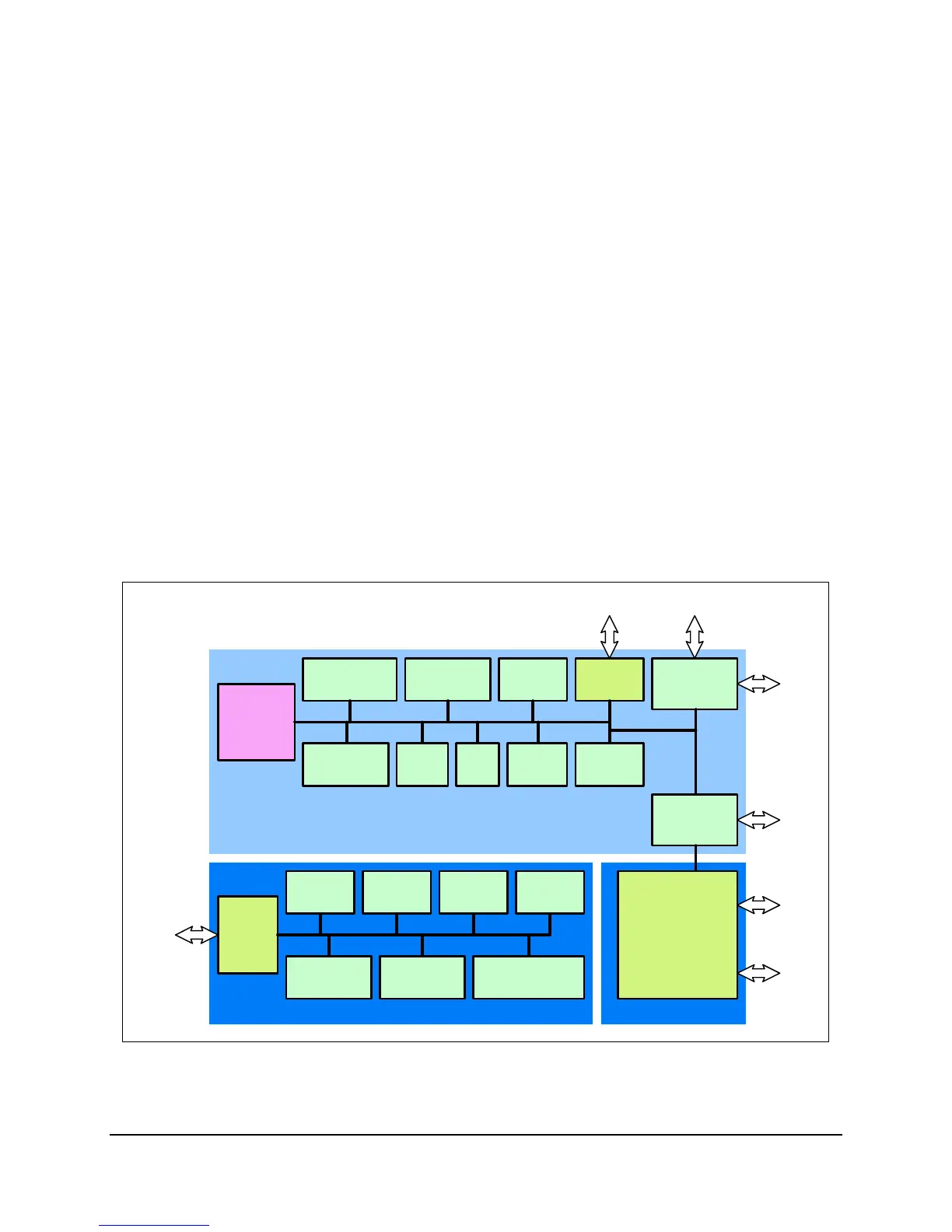

ARM926EJ-S

16K D & I

Cache

Interrupt

Controller

Fan Tach (12)

PWM (4)

ADC

Thermal

USB 1.1

&

USB 2.0

LPC Master,

JTAG Master,

& SPI FLash

UART (3) GPIO

KCS

BT &

Mailboxes

System

Wakeup

Control

LPC

Interface

Graphics

Controller

BMC & KVMS Subsystem

BMC & KVMS Subsystem Graphics Subsystem

RTC &

General Purpose

TImers (3)

UART

(3)

I2C

(6)

Ethernet

MAC with

RMII (2)

Crypto

Accelerator

DDR-II

16-bit

Memory

Controller

LPC to SPI

Flash Bridge

Watchdog

Timer

Real Time Clock

Interface

(external RTC)

LPC

Interface

To Host

Video

Output

PCIe x1

Interface

DDR-II

(up to

667MHz)

JTAG

Master

Code

Memory

USB

to Host

Integrated BMC Block Diagram

Loading...

Loading...