iPECS-MG

Hardware Description and Installation Manual Issue 1.1

48

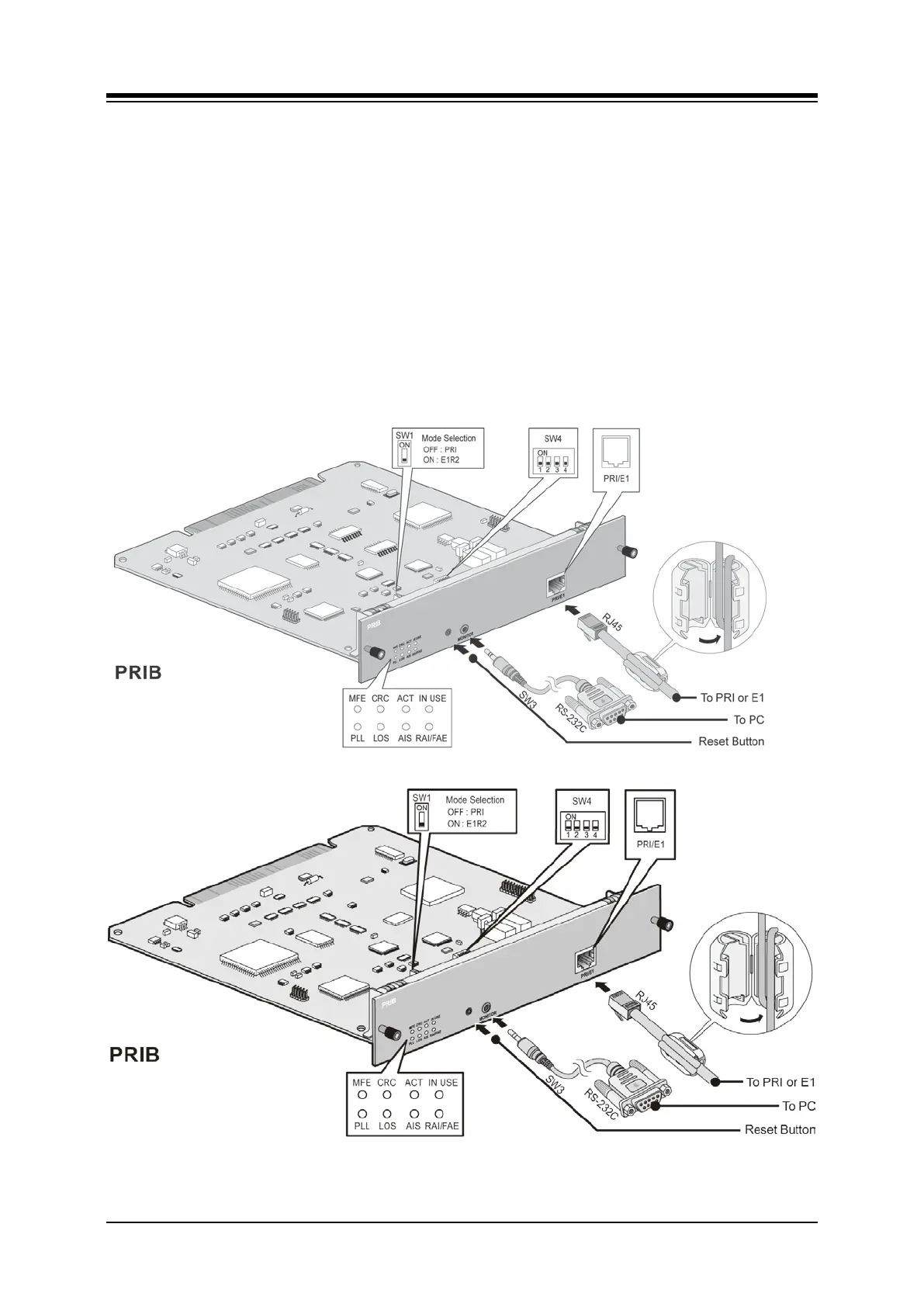

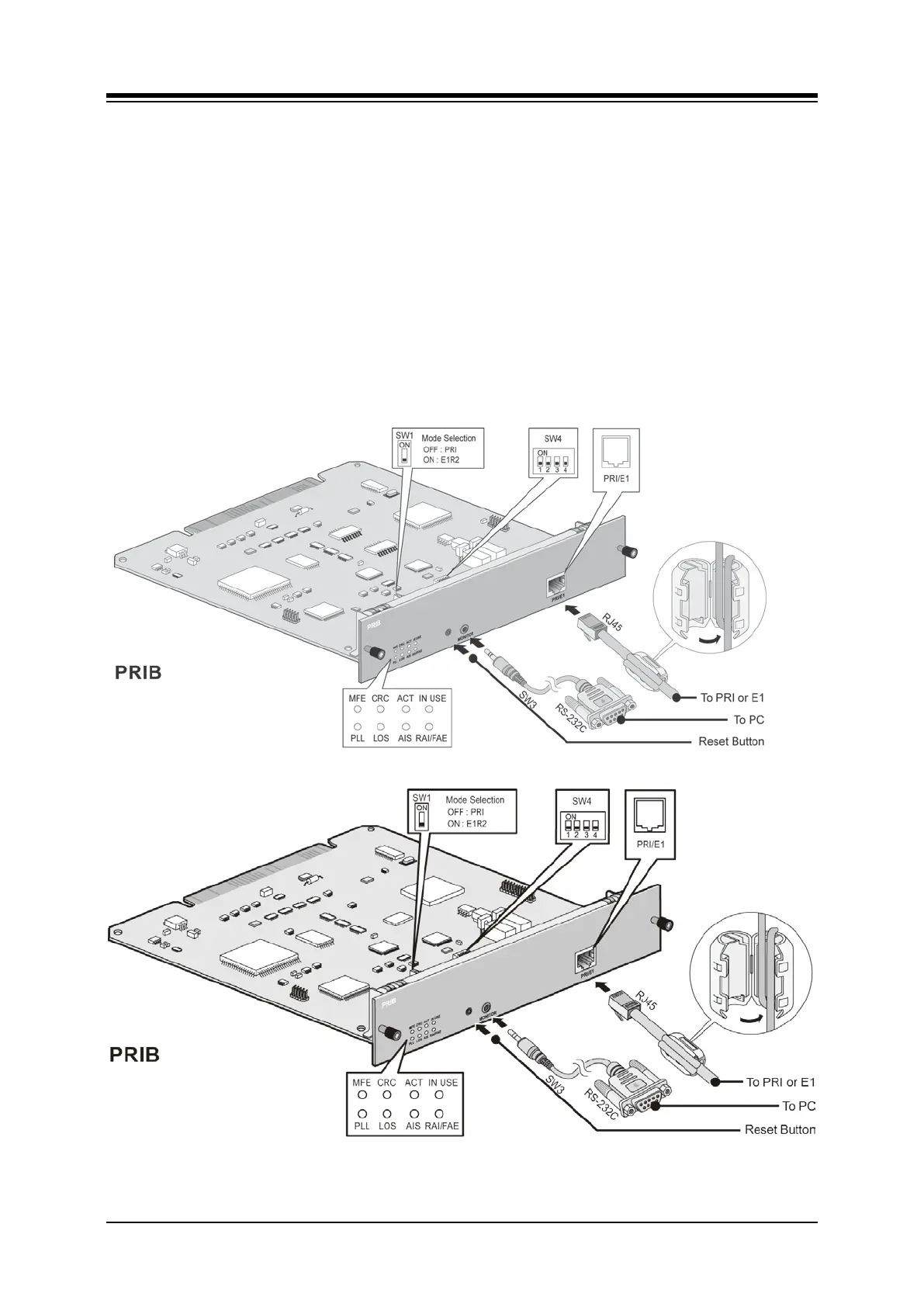

5.3.3 E1R2-PRIB (Primary Rate Interface Board)

There are two kinds of PRIB according to CPU, but they have the same functions.

The Primary Rate Interface Board (PRIB) provides one (1) PRI interface, or one (1) E1R2

interface. The PRI interface supports 30 PCM bearer and 2 signaling channels for PRI or E1R2.

The PRIB is based on the interface described in ITU-T Recommendations G.704, G.703, and

G.823. It covers CEPT frame format that consist of 32 8-bit timeslots, a data rate of 2.048MHz.

From the 32 timeslots in a frame, 30 timeslots are defined as information channels, timeslots 1-

15 and 17-31 that correspond to telephone channels 1-30. The frame has duration of 125ųsec

and contains 32 Time Slots (TS). Time Slot 0 is allocated to frame alignment sync, and Time

Slot 16 is allocated to the signaling channel; the other time slots are available for allocation to

the B channel. The CEPT frame has four signaling bits, A, B, C and D. Signaling bits for all 30

media channels are transmitted in timeslot 16. The PRIB supports pulse dialing, DTMF dialing,

and MFC-R2 register signaling (based on ITU-T Recommendation Q.440-480).

Figure 5.3.3-1 E1-PRIB

Loading...

Loading...