Theory of Operation: Transceiver Board 3-7

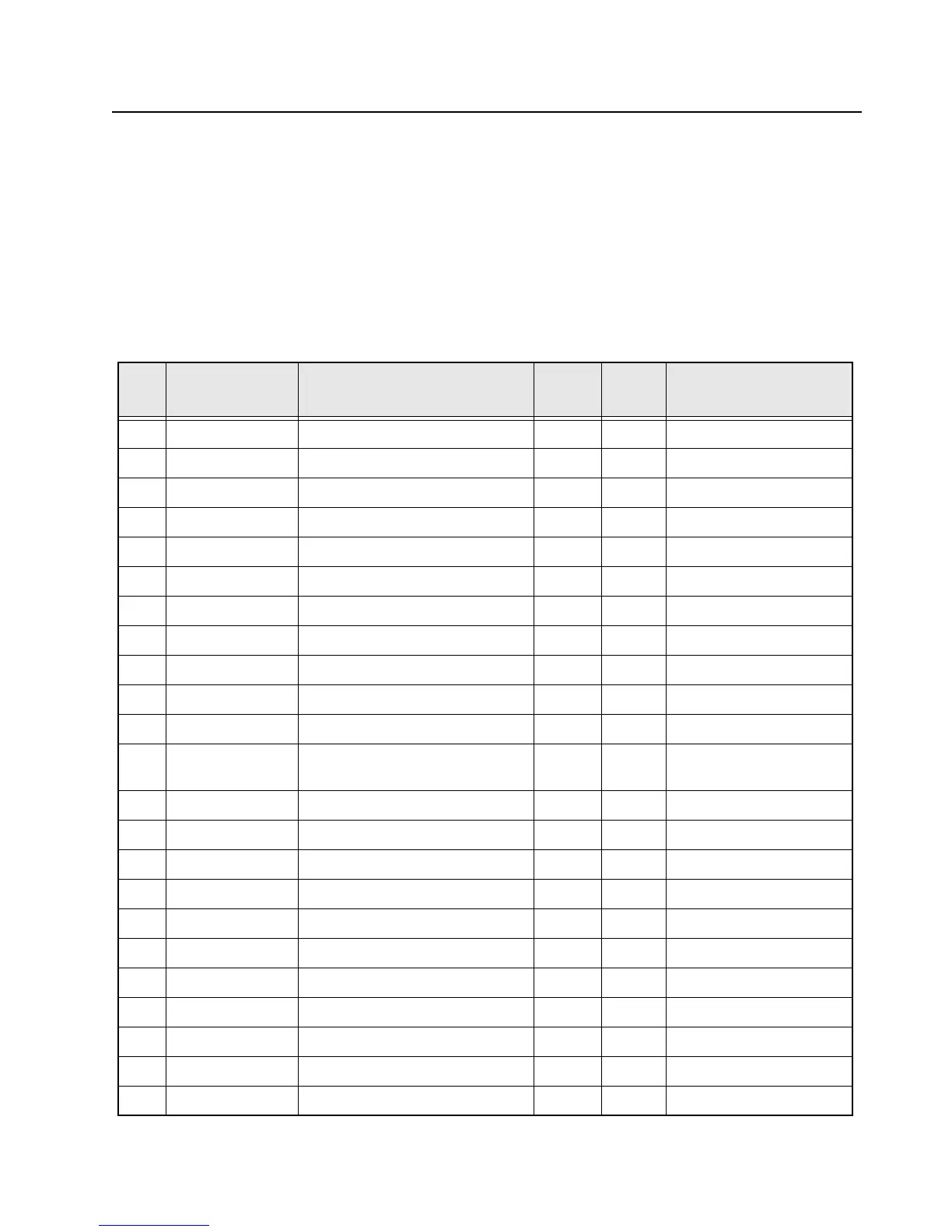

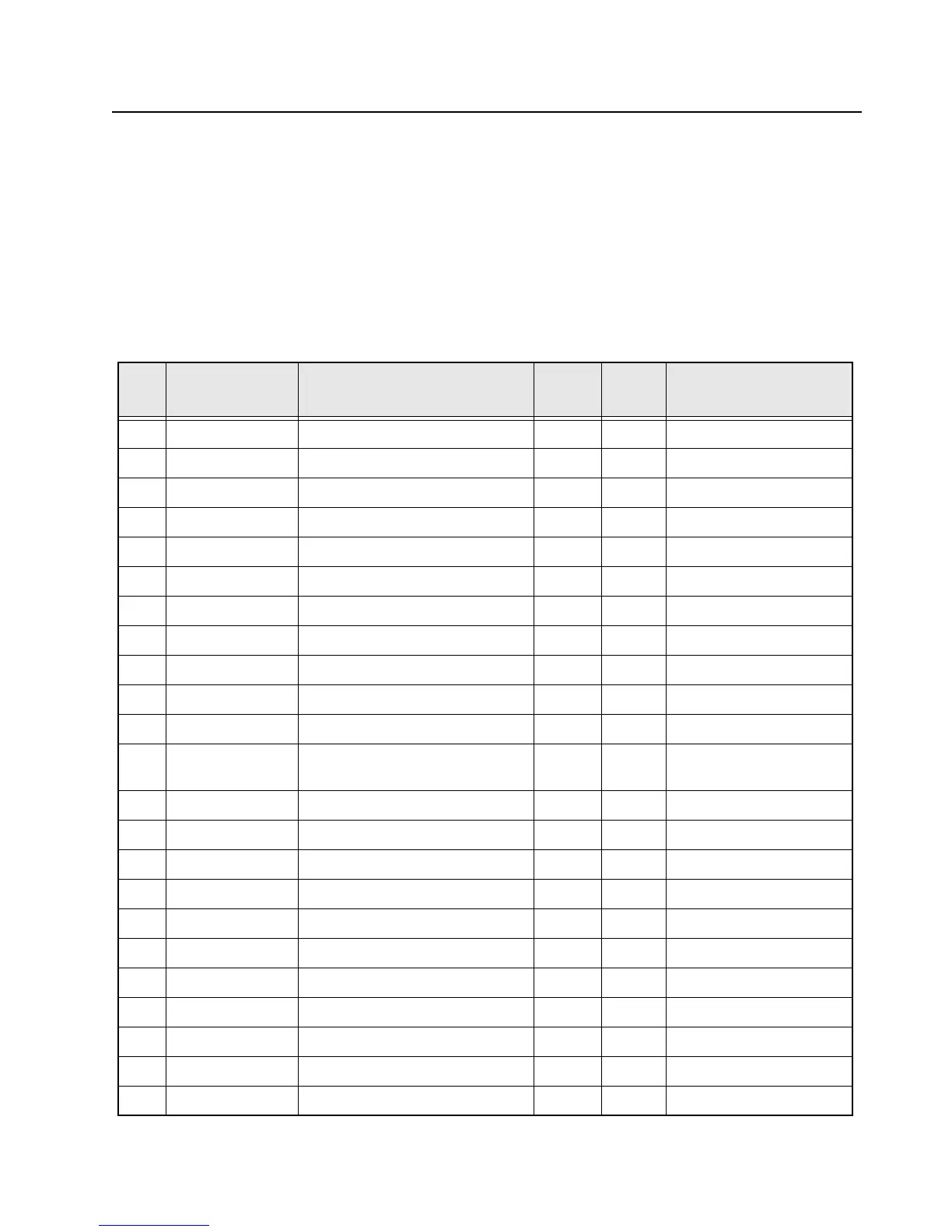

3.1.1.2 VOCON Connector J1001

VOCON connector J1001 is a 40 pin board to board connector that connects to XCVR board

connector P101. This is a digital interface carrying DC power, control, and data between the XCVR

and VOCON boards.

Table 3-2 lists the connector pins, their signals, and functions. SPI refers to serial peripheral

interface, which is the control bus from the microprocessor. SSI is the serial synchronous interface

bus for data to and from the DSP. There is a RX SSI bus for demodulated data from the receiver and

a TX SSI bus for modulation data to the transmitter.

Table 3-2. VOCON Connector J1001

Pin

No.

VOCON Signal XCVR Signal

XCVR

I/O

Type Description

1 GROUND GROUND – – –

2 EEPROM_CS DIG_CTRL_SPI_EEPROM_PE I spi SPI EEprom chip select

3 CLK_16.8MHZ CLK_16_8MHZ O rf 16.8 MHz reference clock

4 GROUND GROUND – – –

5 GROUND GROUND – – –

6 VCC_1.875 DC_LIN_1_875_D I dc Regulated 1.875 V

7 RF_BRD_RSTB DIG_CTRL_RSTB I/O control Reset

8 VCC_2.775 DC_LIN_2_775V I dc Regulated 2.775 V

9 DMCS DIG_CTRL_SSI_TRIGGER I ssi SSI Trigger

10 F2_PARAMP DIG_CTRL_IO49 I control TX Slot enable

11 RX_FSYNC DIG_DATA_SSI_RX_FS O ssi RX SSI frame sync

12 TX_INH DIG_CTRL_TX_INHIBIT_TYPE_1 I control TX inhibit control for

secure

13 RX_DA DIG _DATA _SSI _RX _DOUTA O ssi RX SSI data

14 DAC_CS DIG_CTRL_SPI_DAC_PE I spi SPI DAC chip select

15 RX_CLK CLK_SSI_RX O ssi RX SSI clock

16 ISET ANA_CTRL_ISET I control Mako Ramp

17 TX_FSYNC DIG_TX_SSI_FS I ssi TX SSI frame sync

18 TX_DA_CONN DIG_DATA_TX_SSI I ssi TX SSI data

19 TX_CLK DIG_TX_SSI_CLK I ssi TX SSI clock

20 GROUND GROUND – – –

21 GPS_ANT RF_GPS O rf GPS_RF signal

22 ABACUS_CS DIG_CTRL_SPI_ABACUS_PE I spi SPI Abacus chip select

23 F2_SYNCB DIG_SYNCB I control Synchronize RX SSI data

Loading...

Loading...