5.7 Status System

5-77 ZM2371/ZM2372

5.7.3 Standard Event Status

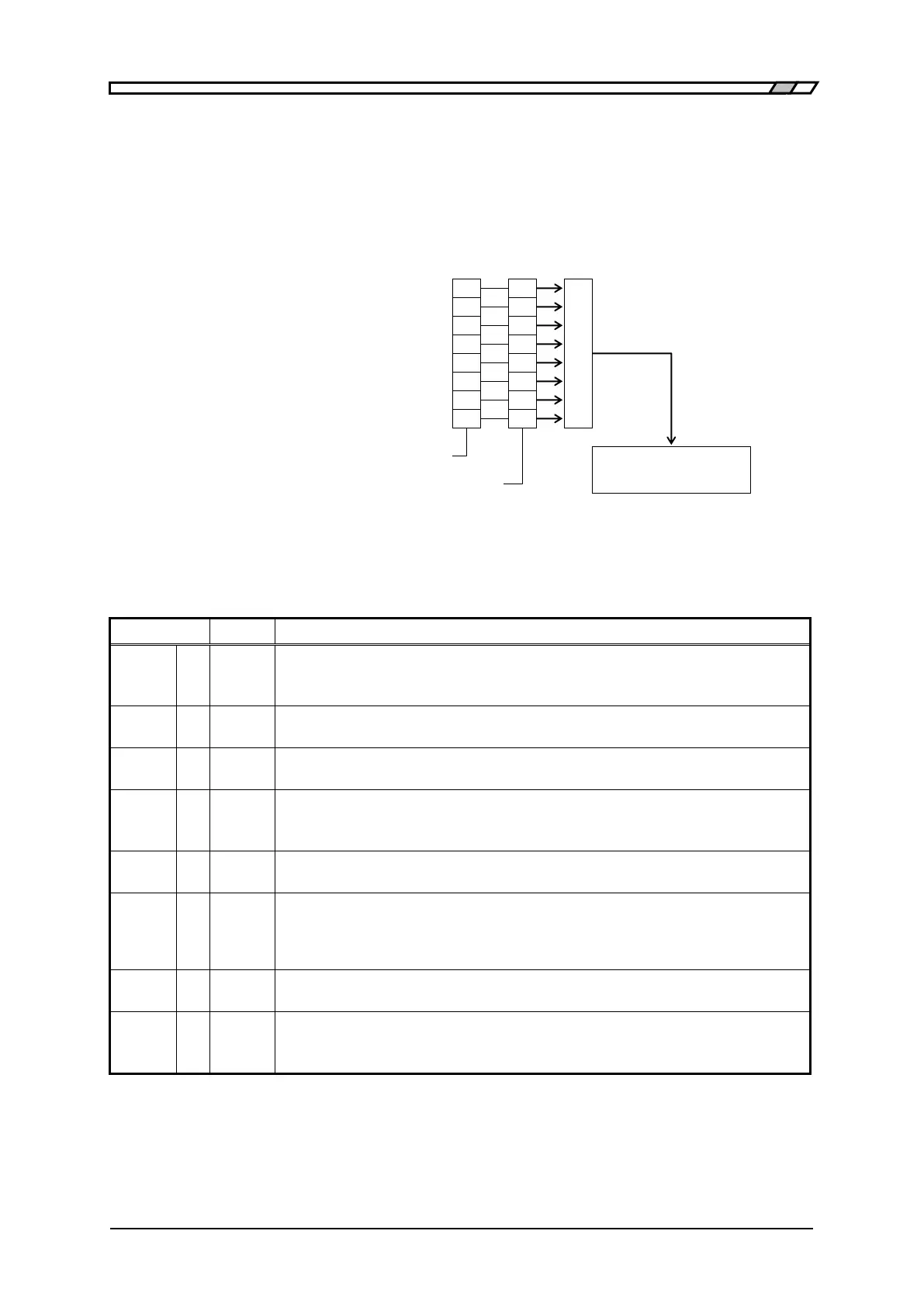

The standard event status structure is shown on Fgure 5-3. Details about status are shown

in Table 5-5. When the standard event status enable register bits are set to 1, the

corresponding standard event status register bits become valid. When at least one such bit

is set to 1, the status bit register ESB bit is set to 1.

Figure 5–3 Standard event status structure

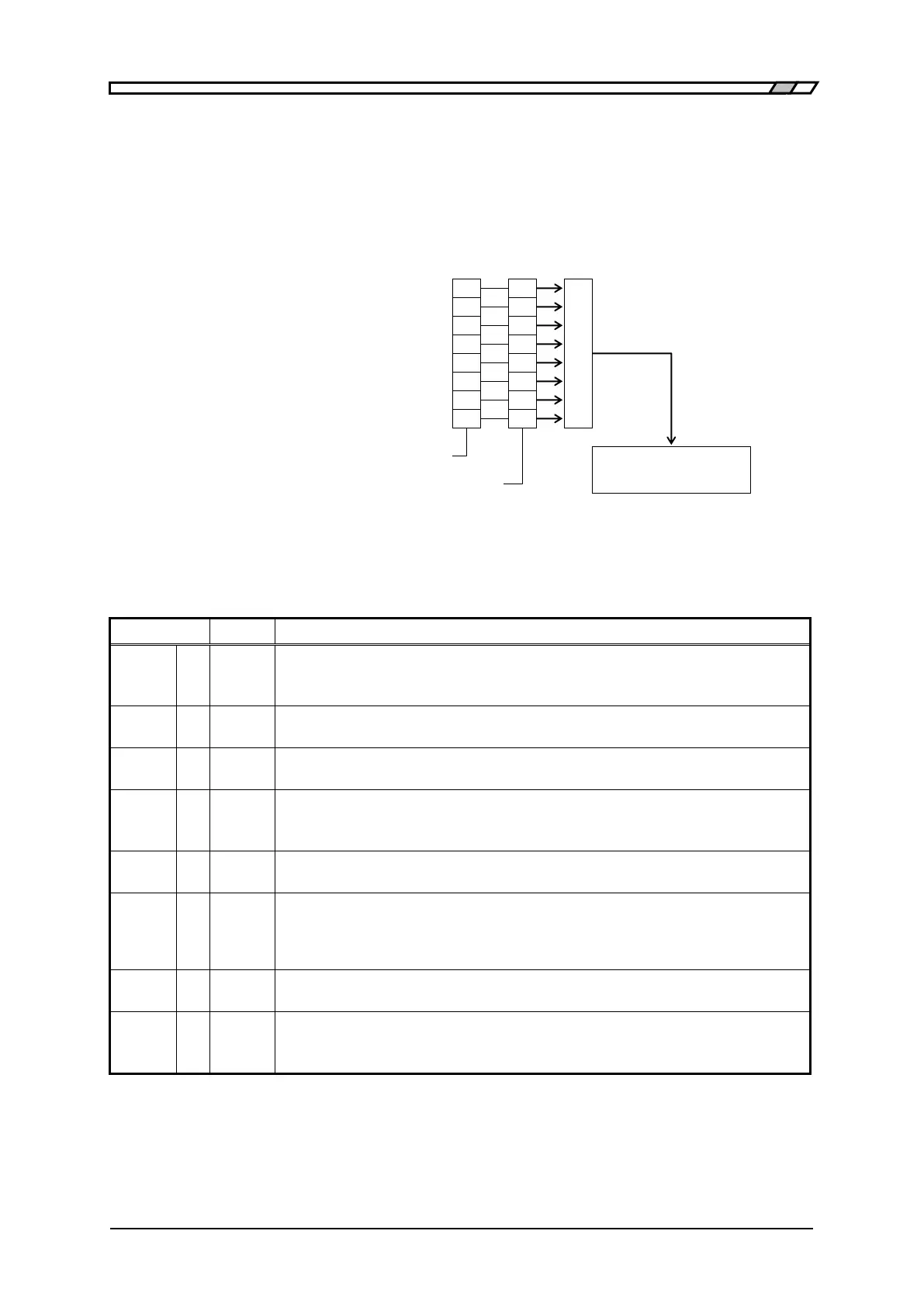

Table 5–5 Standard event status register contents

Power on

Set to 1 when the power is on. If set to 0 by a register readout,

remains at 0 until the power is turned on again.

User request

Always at 0 (unused)

Command error

Set to 1 when there is a syntax error in program code.

Execution error

Set to 1 when parameters are set beyond possible range values or

when settings are contradictory.

Device dependent error

Set to “1” when the error queue overflows.

Query error

Set to 1 when a readout has been attempted on an empty response

message output buffer or when the response message output buffer

data has been lost.

Request control

Always at 0 (unused)

Operation complete

Set to “1” when a processing of all commands up to *OPC command

completed.

Power on PON

Always at 0 (unused) URQ

Command error CME

Execution error EXE

Always at 0 (unused) DDE

Query error QYE

Always at 0 (unused) RQC

Operation complete (OPC)

(Standard event status register) ESR

(Standard event status enable register) ESE

Standard event status

summary

Loading...

Loading...