B

Control Equations & Relay Logic

SIMPRO-100

142 PRIM-2400C

B.4.1 Control Equation

Operators

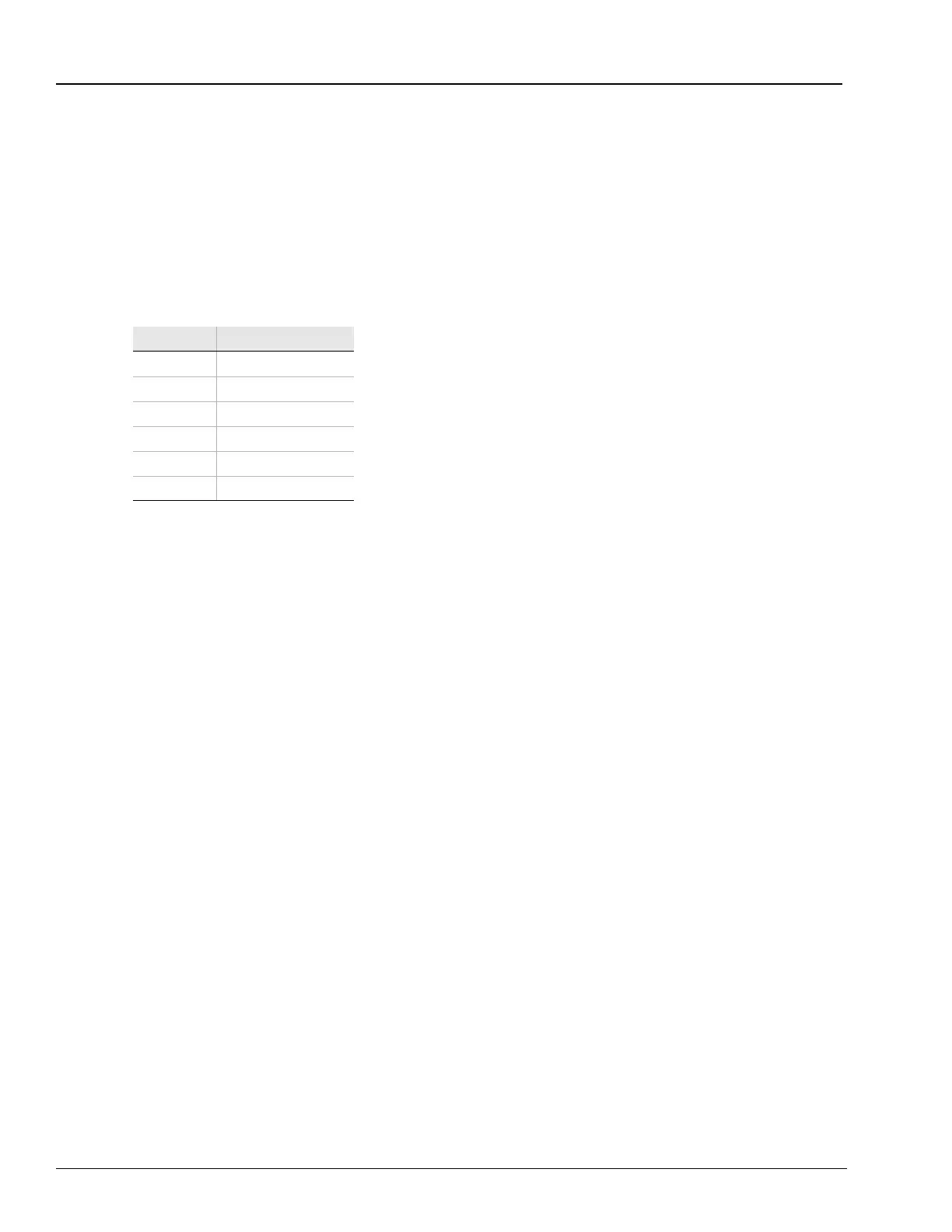

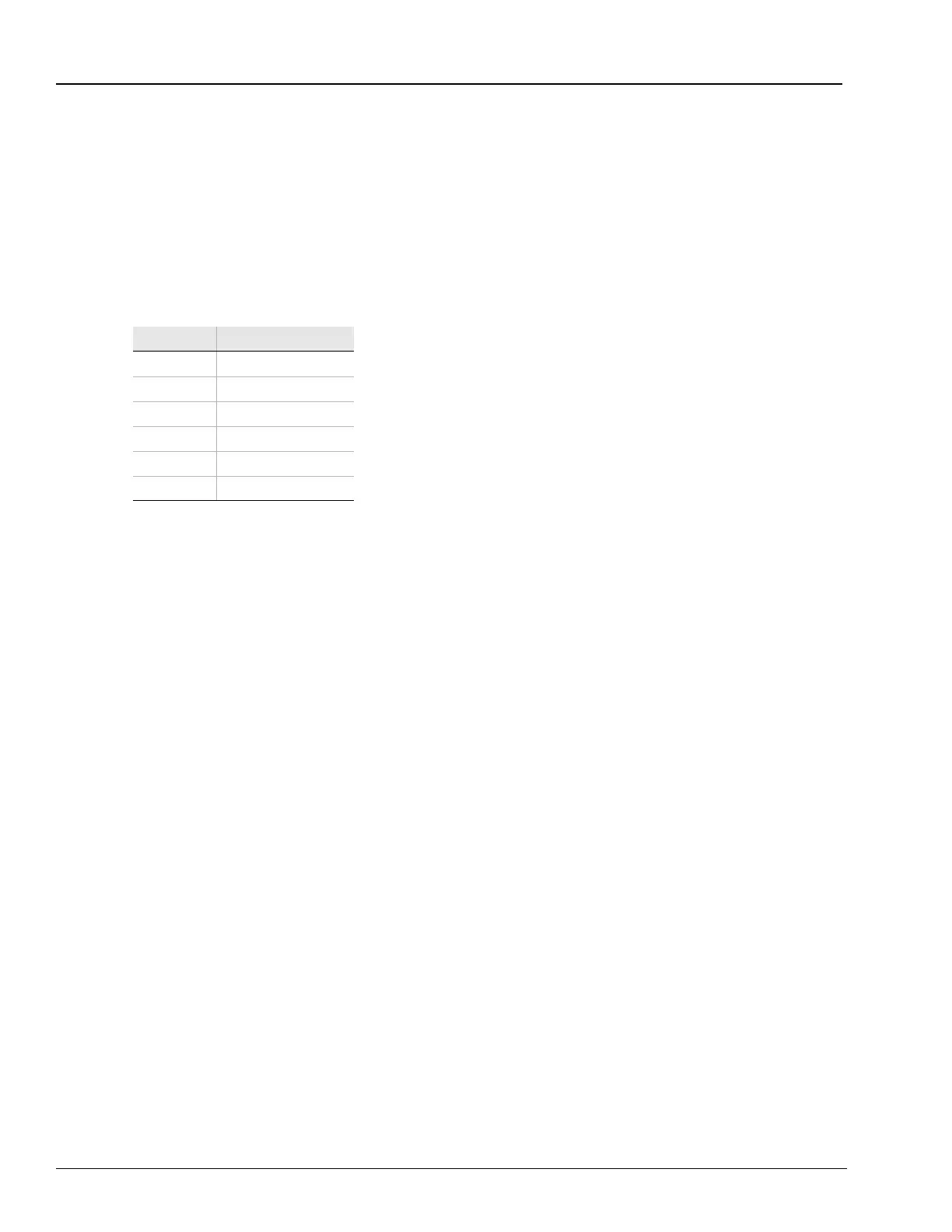

Build control equation settings using logic similar

to Boolean algebra logic, by combining Relay

Word bits together using one or more of the six

control equation operators listed in Table B.3.

These operators are processed in a control

equation in the order shown in Table B.3.

Table B.3 Control Equation Operators

B.4.1.1 Control Equation AND

Operator [*]

Use the asterisk [*] symbol to denote logical AND

operations. When you use the [*] between two

Relay Word bits, both must pick up in order for

the relay to perform the operation in question. For

instance, if SV1 is the equation that controls

control equation variable 1, you could set SV1

equal to:

Equation B.1

With this setting, SV1 is true, or logical 1, when

both 50P1T and IN4 are true. Any number of

Relay Word bits may be ANDed together within

an equation, subject to the overall limitations

described in Section B.4.3, page 144.

B.4.1.2 Control Equation OR

Operator [+]

Use the plus [+] symbol to denote logical OR

operations. When you use the [+] between two

Relay Word bits, either can pick up to cause the

relay to perform the operation in question. For

instance, if SV1 is the equation controlling control

equation variable 1, you could set SV1 equal to:

Equation B.2

With this setting, SV1 is true, or logical 1, when

either 50P1T or 50P2T are picked up. Any

number of Relay Word bits may be ORed

together within an equation, subject to the overall

limitations described in Section B.4.3, page 144.

B.4.1.3 Control Equation Falling-Edge

Operator [\]

Use the falling-edge operator [\] with individual

Relay Word bits to cause a single

processing-cycle assertion when the Relay Word

bit changes state from logical 1 to logical 0. The

falling-edge operator [\] looks for Relay Word bit

deassertion (element going from logical 1 to

logical 0). The falling-edge operator [\] in front of

a Relay Word bit sees this logical 1 to logical 0

transition as a falling-edge and asserts to logical

1 for one processing interval. Do not apply the [\]

operator to groups of elements within

parentheses.

For example, suppose the control equation event

report generation setting is set with the detection

of the falling-edge of an underfrequency element:

Equation B.3

Operator Logic Function

/ Rising edge detect

\ Falling edge detect

( ) parentheses

!NOT

*AND

+OR

SV1 = 50PIT * IN4

SV1 = 50PIT + 50P2T

ER = ... + \81D1T

Loading...

Loading...