RM0440 Rev 4 1301/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

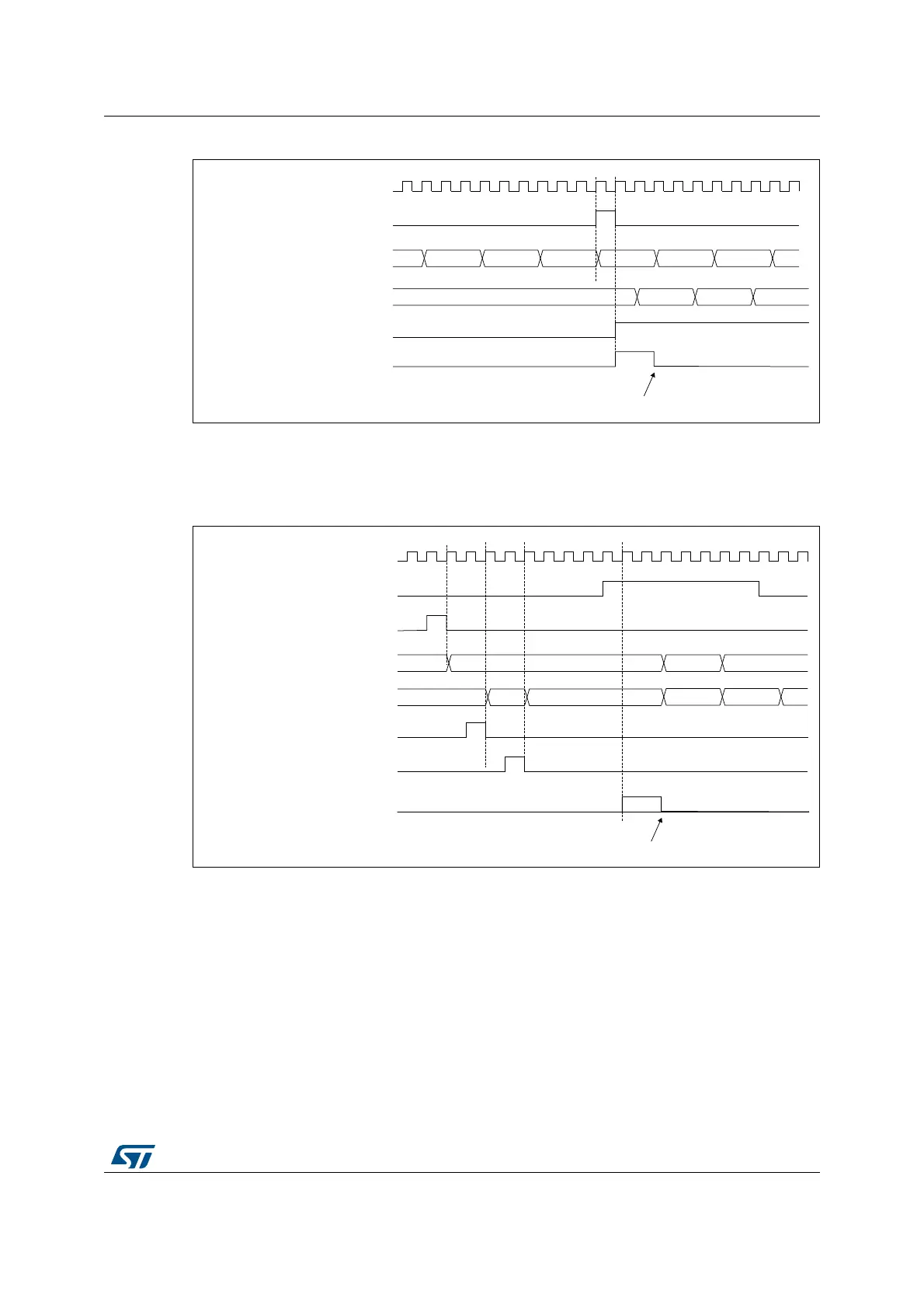

Figure 436. Triggering TIM_slv with update of TIM_mstr

As in the previous example, both counters can be initialized before starting counting.

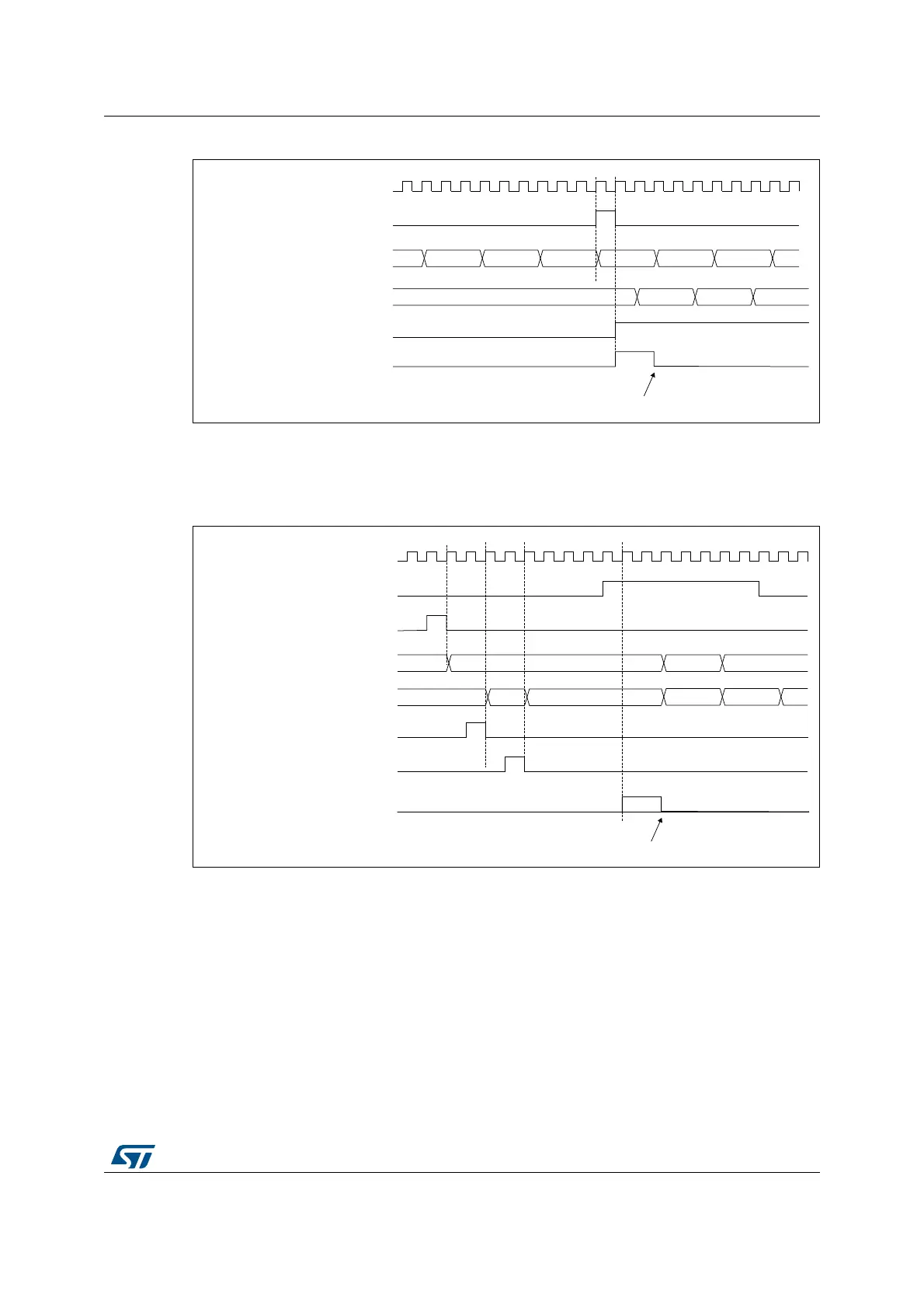

Figure 437 shows the behavior with the same configuration as in Figure 436 but in trigger

mode instead of gated mode (SMS=110 in the TIM_slv_SMCR register).

Figure 437. Triggering TIM_slv with Enable of TIM_mstr

Starting 2 timers synchronously in response to an external trigger

In this example, we set the enable of TIM_mstr when its tim_ti1 input rises, and the enable

of TIM_slv with the enable of TIM_mstr. Refer to Figure 432 for connections. To ensure the

counters are aligned, TIM_mstr must be configured in Master/Slave mode (slave with

respect to tim_ti1, master with respect to TIM_slv):

MSv62378V1

tim_ker_ck

tim_slv_CNT

FD

tim_mst_CNT

Write TIF = 0

TIM_slv counter enable (CEN bit)

tim_slv TIF bit

FE FF 00 01 02

46 47 4845

tim_mstr UEV

event

MSv62379V1

tim_ker_ck

tim_slv_CNT

tim_mstr_CNT reset

Write TIF = 0

TIM_mst counter enable (CEN bit)

tim_slv TIF bit

E7

0200 01

E9

75

CD 00 E8 EA

tim_mstr_CNT

tim_slv_CNT reset

Tim_slv_CNT write

Loading...

Loading...