RM0440 Rev 4 1943/2126

RM0440 System window watchdog (WWDG)

1943

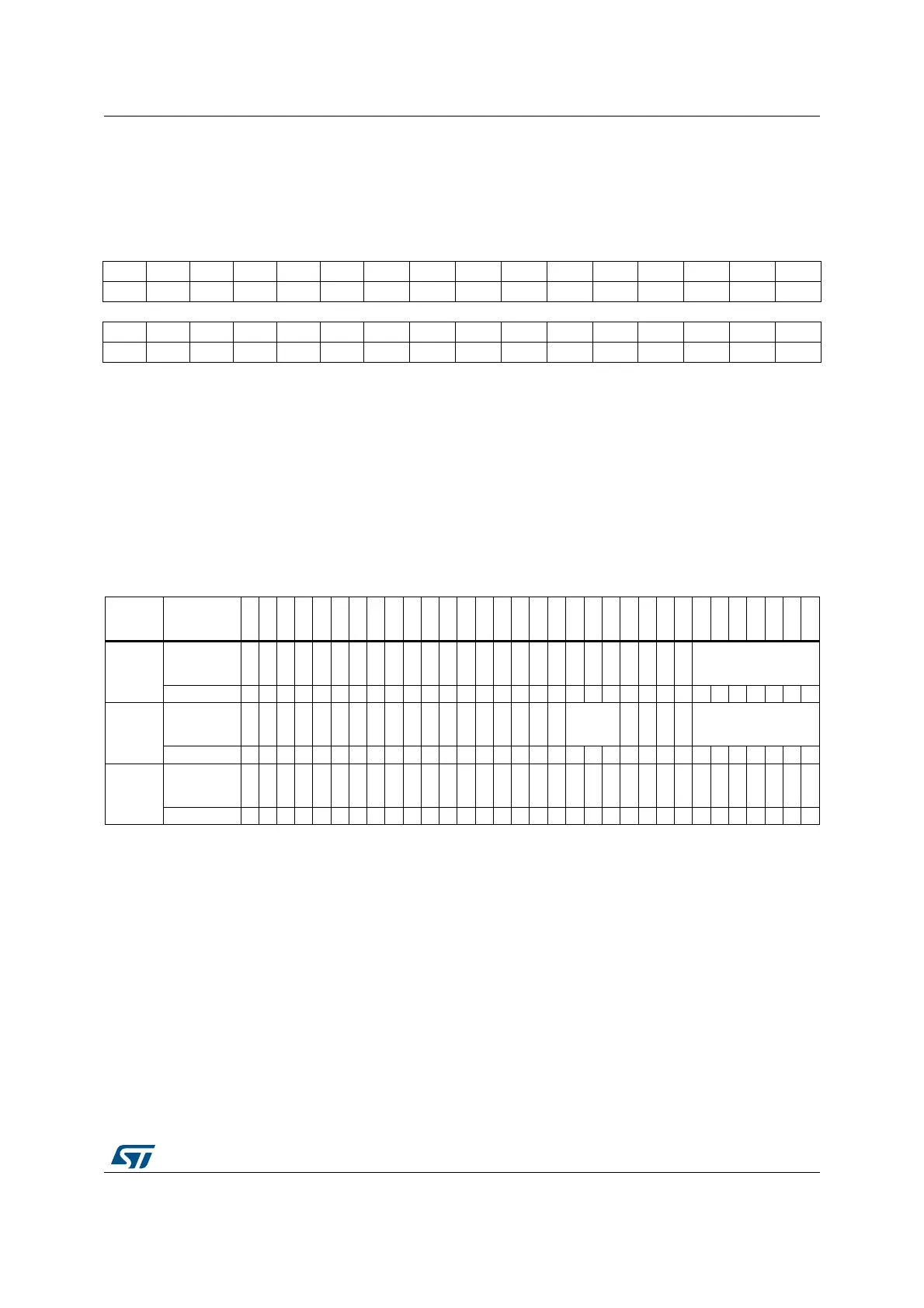

43.5.3 WWDG status register (WWDG_SR)

Address offset: 0x008

Reset value: 0x0000 0000

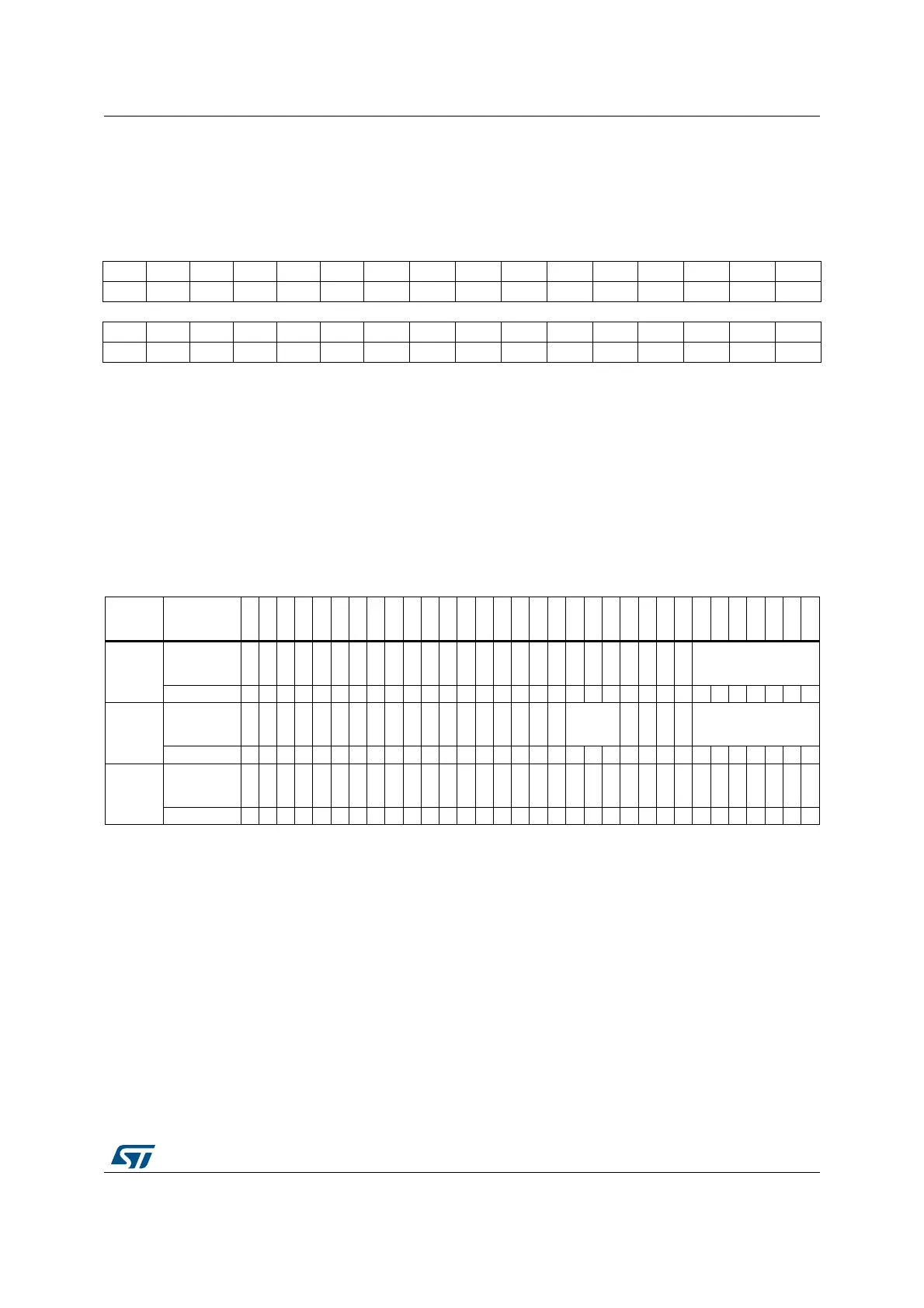

43.5.4 WWDG register map

The following table gives the WWDG register map and reset values.

Refer to Section 2.2 on page 80 for the register boundary addresses.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. EWIF

rc_w0

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 EWIF: Early wakeup interrupt flag

This bit is set by hardware when the counter has reached the value 0x40. It must be cleared

by software by writing ‘0’. Writing ‘1’ has no effect. This bit is also set if the interrupt is not

enabled.

Table 392. WWDG register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x000

WWDG_CR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

WDGA

T[6:0]

Reset value 01111111

0x004

WWDG_CFR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

WDGTB

[2:0]

Res.

EWI

Res.

Res.

W[6:0]

Reset value 000 0 1111111

0x008

WWDG_SR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

EWIF

Reset value 0

Loading...

Loading...