RM0440 Rev 4 1895/2126

RM0440 Inter-integrated circuit (I2C) interface

1928

Packet error checking

A packet error checking mechanism has been introduced in the SMBus specification to

improve reliability and communication robustness. Packet Error Checking is implemented

by appending a Packet Error Code (PEC) at the end of each message transfer. The PEC is

calculated by using the C(x) = x

8

+ x

2

+ x + 1 CRC-8 polynomial on all the message bytes

(including addresses and read/write bits).

The peripheral embeds a hardware PEC calculator and allows a Not Acknowledge to be

sent automatically when the received byte does not match with the hardware calculated

PEC.

Timeouts

This peripheral embeds hardware timers in order to be compliant with the 3 timeouts defined

in SMBus specification.

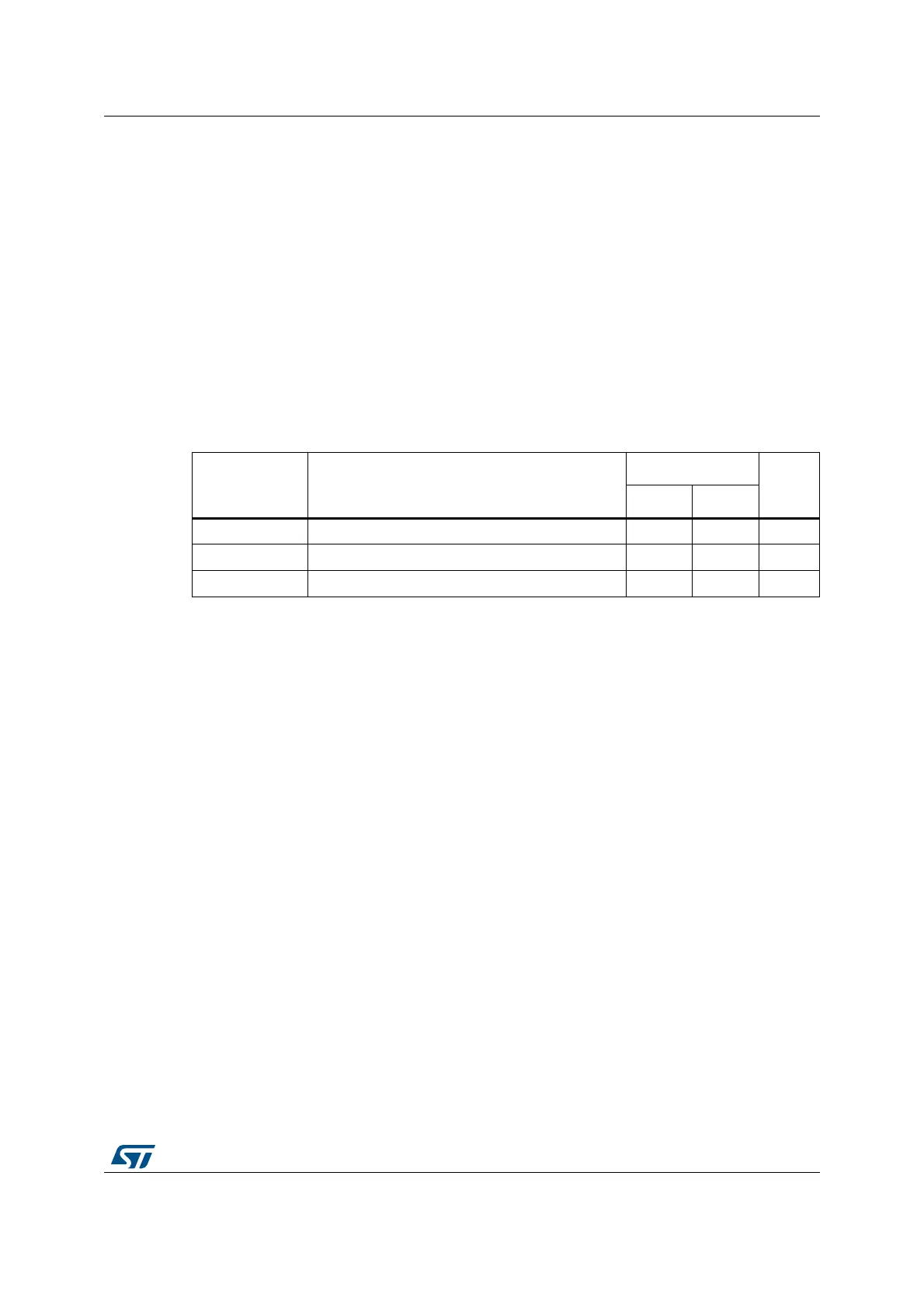

Table 383. SMBus timeout specifications

Symbol Parameter

Limits

Unit

Min Max

t

TIMEOUT

Detect clock low timeout 25 35 ms

t

LOW:SEXT

(1)

1. t

LOW:SEXT

is the cumulative time a given slave device is allowed to extend the clock cycles in one message

from the initial START to the STOP. It is possible that, another slave device or the master also extends the

clock causing the combined clock low extend time to be greater than t

LOW:SEXT

. Therefore, this parameter is

measured with the slave device as the sole target of a full-speed master.

Cumulative clock low extend time (slave device) - 25 ms

t

LOW:MEXT

(2)

2. t

LOW:MEXT

is the cumulative time a master device is allowed to extend its clock cycles within each byte of a

message as defined from START-to-ACK, ACK-to-ACK, or ACK-to-STOP. It is possible that a slave device

or another master also extends the clock causing the combined clock low time to be greater than t

LOW:MEXT

on a given byte. Therefore, this parameter is measured with a full speed slave device as the sole target of

the master.

Cumulative clock low extend time (master device) - 10 ms

Loading...

Loading...