Power control (PWR) RM0440

242/2126 RM0440 Rev 4

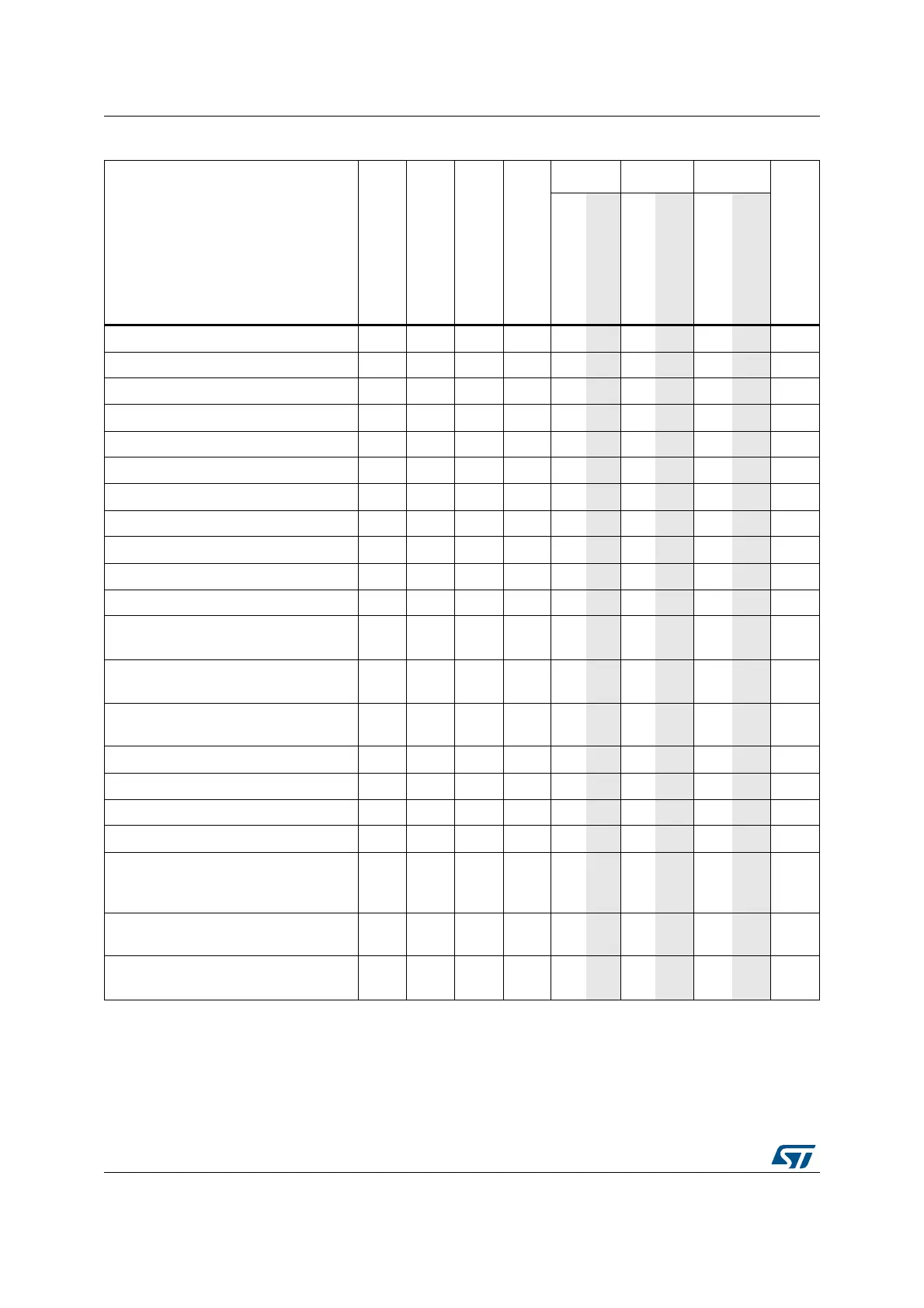

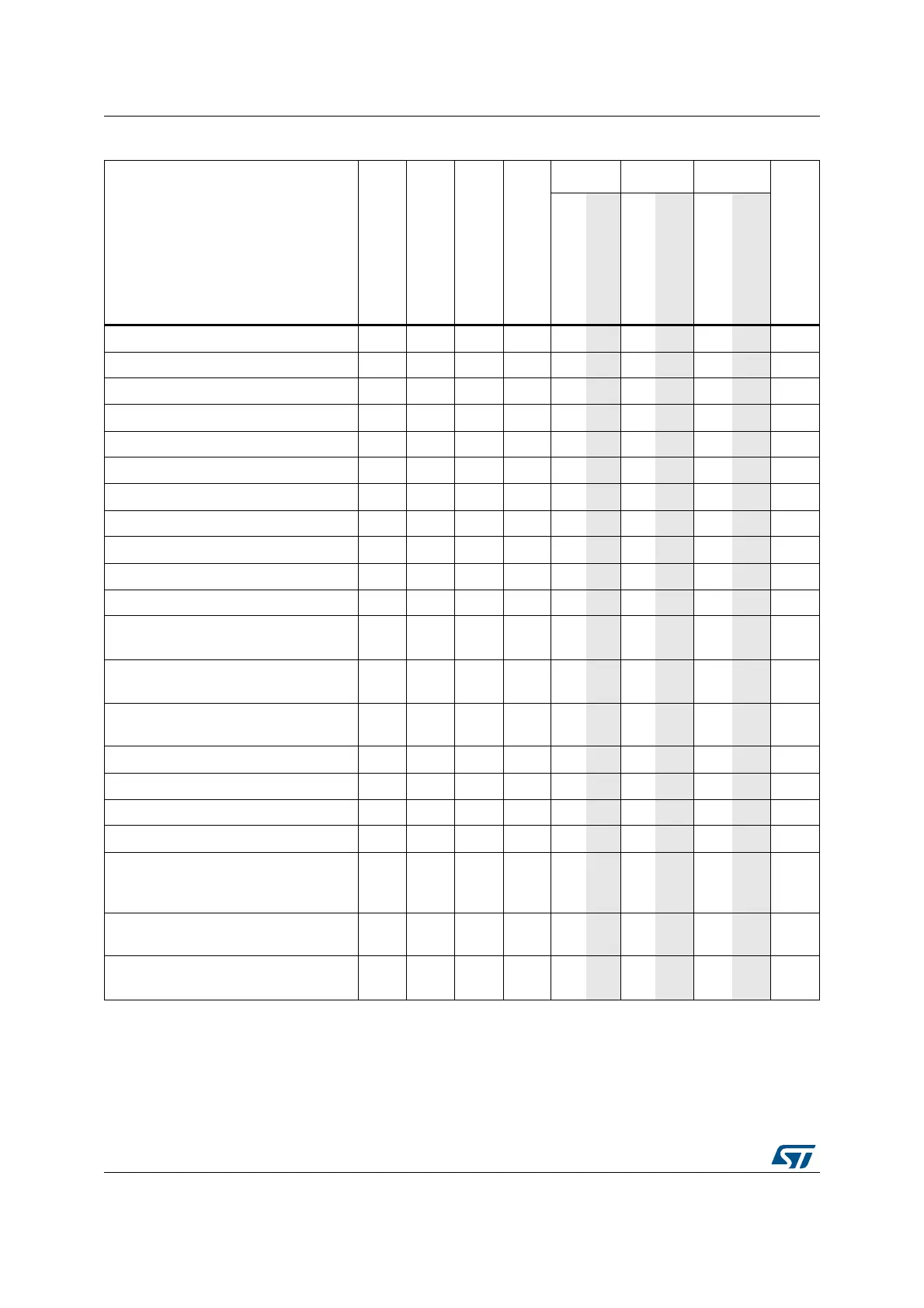

SPIx (1,2,3,4) O O O O - -- ----

FDCANx (1,2,3) O O O O -

-- ----

SAI1 O O O O -

-- ----

ADCx (x=1,2,3,4,5) O O O O -

-- ----

DACx (x=1,2,3,4) O O O O O

-- ----

VREFBUF O O O O O

-- ----

OPAMPx (x=1,2,3,4,5,6) O O O O O

-- ----

COMPx (x=1,2,3,4,5,6,7) O O O O O

O- ----

Temperature sensor O O O O -

-- ----

Timers (TIMx) O O O O -

-- ----

High resolution timer 1 (HRTIM1) O O O O -

-- ----

Low-power timer 1 (LPTIM1) O O O O O O- ----

Independent watchdog (IWDG) O O O O O

OO O- --

Window watchdog (WWDG) O O O O -

-- ----

SysTick timer O O O O - -- ----

Random number generator (RNG) O

(8)

O

(8)

----- ----

AES hardware accelerator O O O O -

-- ----

CRC calculation unit O O O O -

-- ----

GPIOs O O O O O

O

(9)

5

pins

(10)

(11)

5

pins

(10)

-

Filter Mathematical Accelerator (FMAC) O O O O -

-- ----

CORDIC co-processor (CORDIC) O O O O -

-- ----

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available , wakeup

highlighted in gray.

2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

3. The SRAM clock can be gated on or off.

4. SRAM2 content is preserved when the bit RRS is set in PWR_CR3 register.

Table 41. Functionalities depending on the working mode

(1)

(continued)

Peripheral Run Sleep

Low-power run

Low-power sleep

Stop 0/1 Standby Shutdown

VBAT

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

Loading...

Loading...