RM0440 Rev 4 257/2126

RM0440 Power control (PWR)

271

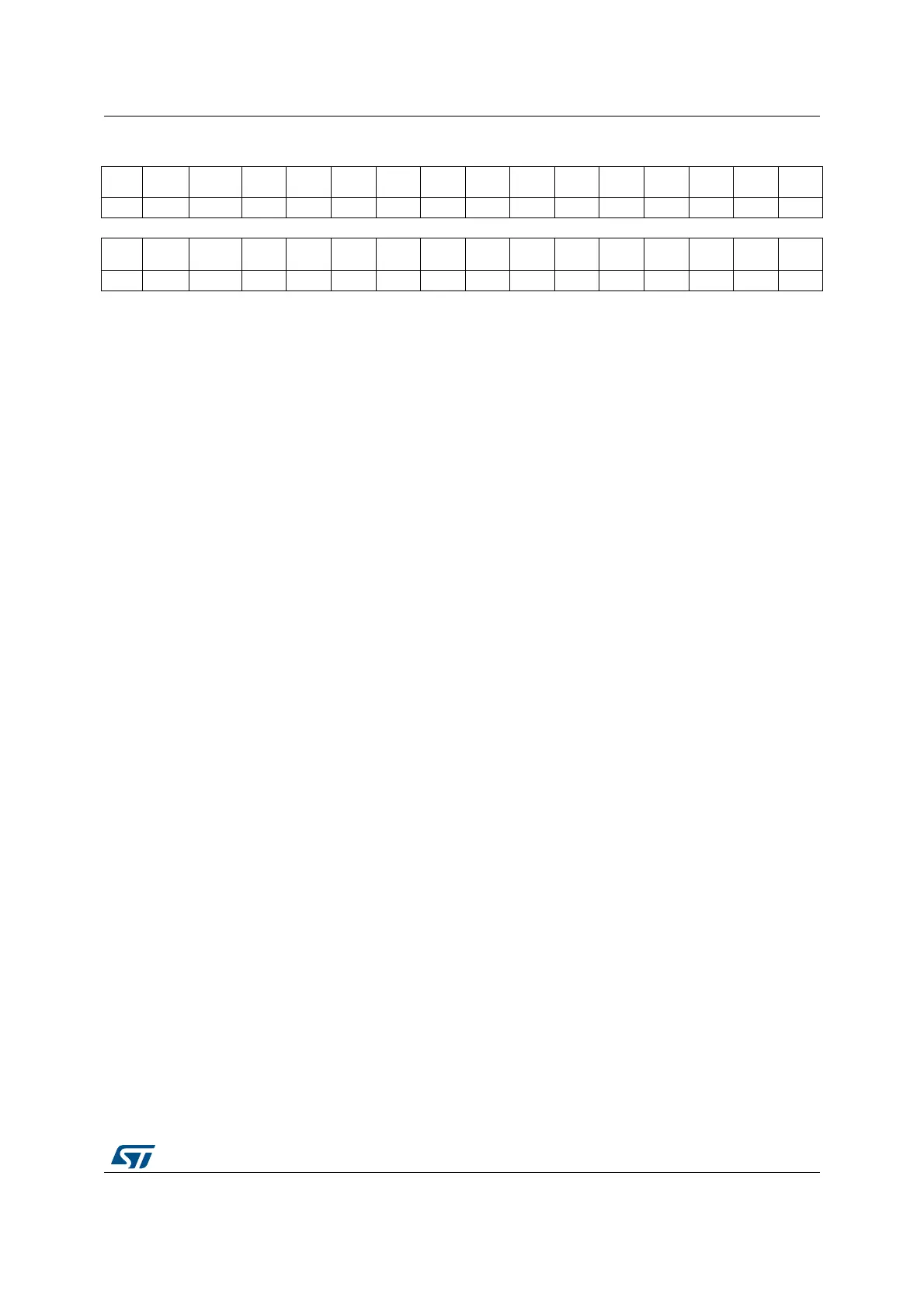

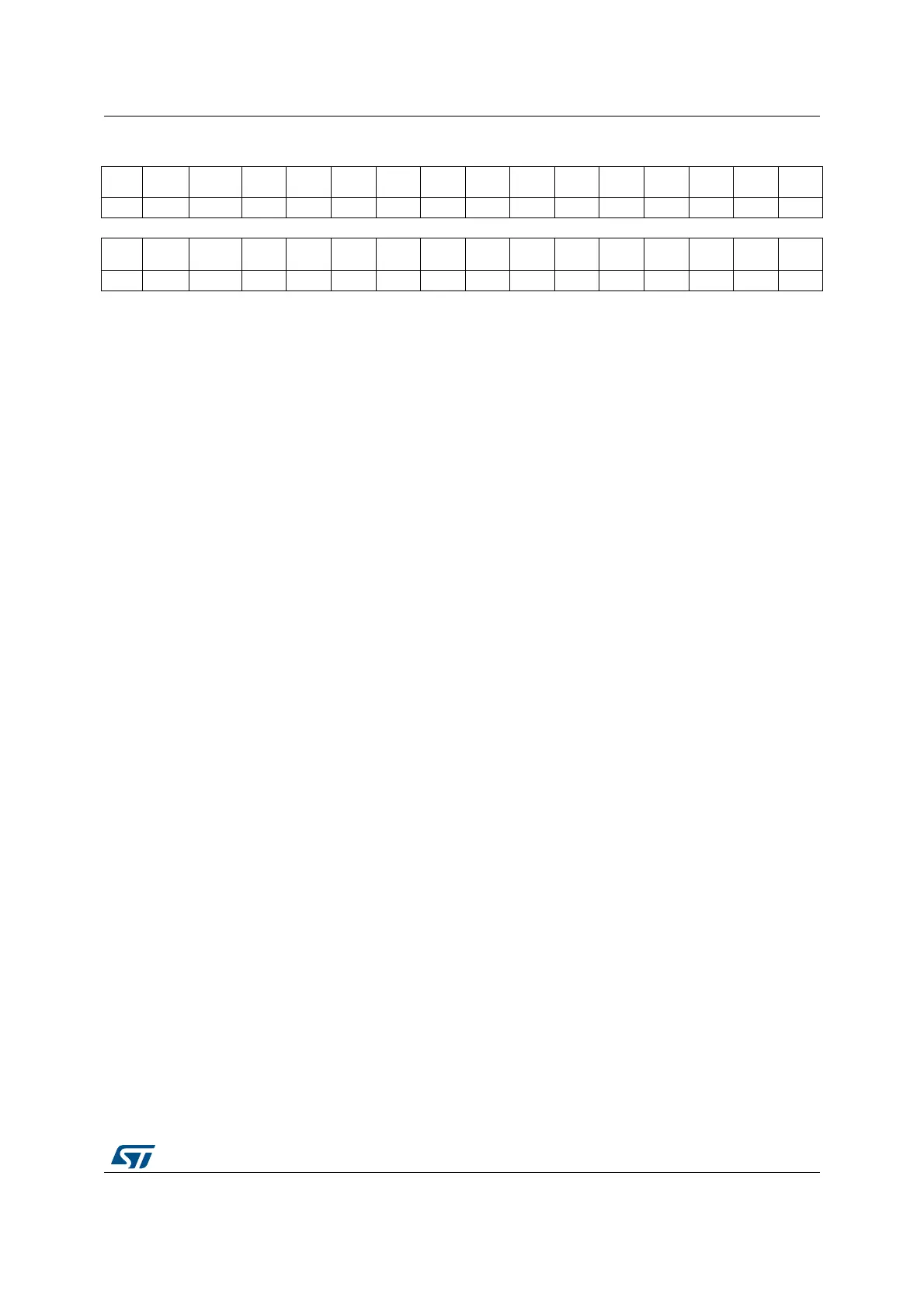

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

EIWUL

UCPD1

_DBDIS

UCPD1_

STDBY

Res. Res. APC Res. RRS Res. Res. Res.

EWUP

5

EWUP

4

EWUP

3

EWUP

2

EWUP

1

rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 EIWUL: Enable internal wakeup line

0: Internal wakeup line disable.

1: Internal wakeup line enable.

Bit 14 UCPD1_DBDIS: USB Type-C and Power Delivery Dead Battery disable.

After exiting reset, the USB Type-C “dead battery” behavior is enabled, which may have

a pull-down effect on CC1 and CC2 pins. It is recommended to disable it in all cases, either

to stop this pull-down or to hand over control to the UCPD1 (which should therefore be

initialized before doing the disable).

0: Enable USB Type-C dead battery pull-down behavior on UCPD1_CC1 and UCPD1_CC2

pins.

1: Disable USB Type-C dead battery pull-down behavior on UCPD1_CC1 and UCPD1_CC2

pins.

Bit 13 UCPD1_STDBY: UCPD1_STDBY USB Type-C and Power Delivery standby mode.

0: Write ‘0’ immediately after standby exit when using UCPD1, (and before writing any

UCPD1 registers).

1: Write ‘1’ just before entering standby when using UCPD1.

Bits 12:11 Reserved, must be kept at reset value.

Bit 10 APC: Apply pull-up and pull-down configuration

When this bit is set, the I/O pull-up and pull-down configurations defined in the PWR_PUCRx

and PWR_PDCRx registers are applied. When this bit is cleared, the PWR_PUCRx and

PWR_PDCRx registers are not applied to the I/Os.

Bit 9 Reserved, must be kept at reset value.

Bit 8 RRS: SRAM2 retention in Standby mode

0: SRAM2 is powered off in Standby mode (SRAM2 content is lost).

1: SRAM2 is powered by the low-power regulator in Standby mode (SRAM2 content is kept).

Bits 7:5 Reserved, must be kept at reset value.

Bit 4 EWUP5: Enable Wakeup pin WKUP5

When this bit is set, the external wakeup pin WKUP5 is enabled and triggers a wakeup from

Standby or Shutdown event when a rising or a falling edge occurs.The active edge is

configured via the WP5 bit in the PWR_CR4 register.

Bit 3 EWUP4: Enable Wakeup pin WKUP4

When this bit is set, the external wakeup pin WKUP4 is enabled and triggers a wakeup from

Standby or Shutdown event when a rising or a falling edge occurs. The active edge is

configured via the WP4 bit in the PWR_CR4 register.

Loading...

Loading...