Reset and clock control (RCC) RM0440

316/2126 RM0440 Rev 4

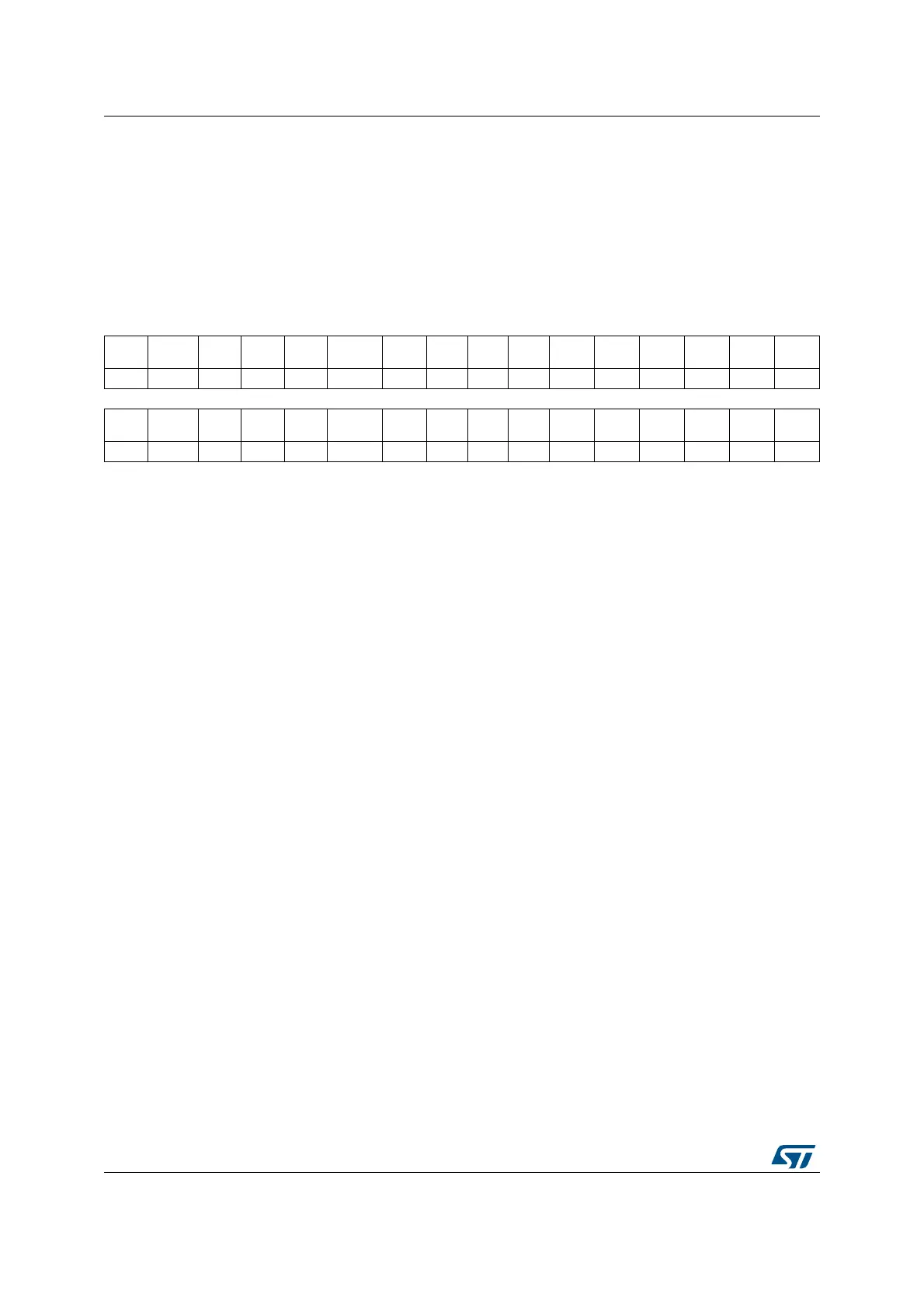

7.4.19 APB2 peripheral clock enable register (RCC_APB2ENR)

Address: 0x60

Reset value: 0x0000 0000

Access: word, half-word and byte access

Note: When the peripheral clock is not active, the peripheral registers read or write access is not

supported.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res.

HRTIM1

EN

Res. Res. Res. Res.

SAI1

EN

TIM20

EN

Res.

TIM

17EN

TIM16

EN

TIM15

EN

rw rw rw rw rw rw

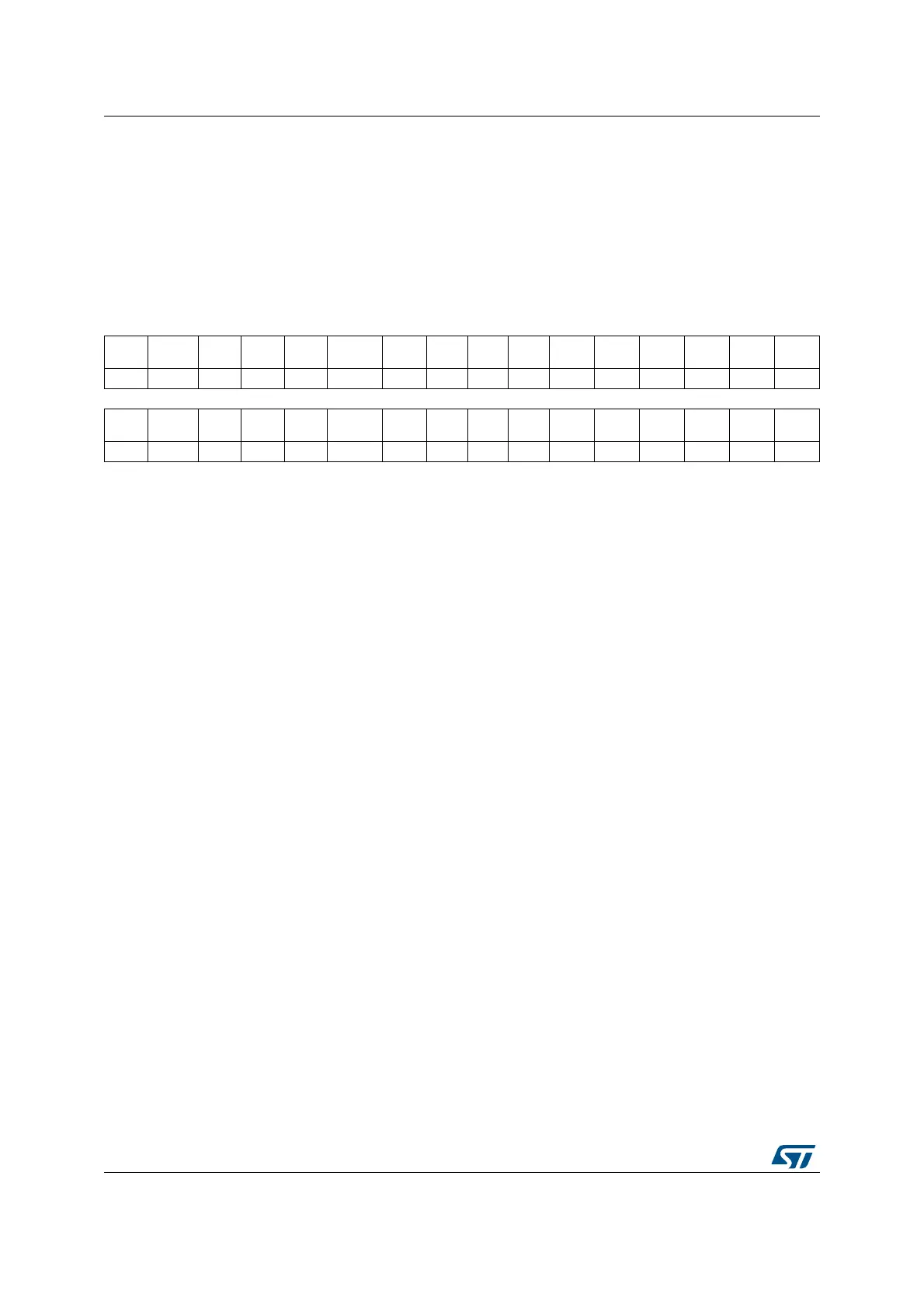

151413121110 9876543210

SPI4

EN

USART1

EN

TIM8

EN

SPI1

EN

TIM1

EN

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

SYS

CFGEN

rw rw rw rw rw rw

Bits 31:27 Reserved, must be kept at reset value.

Bit 26 HRTIM1EN: HRTIM1 clock enable

Set and cleared by software.

0: HRTIM1 clock disabled

1: HRTIM1 clock enable

Bits 25:22 Reserved, must be kept at reset value.

Bit 21 SAI1EN: SAI1 clock enable

Set and cleared by software.

0: SAI1 clock disabled

1: SAI1 clock enabled

Bit 20 TIM20EN: TIM20 timer clock enable

Set and cleared by software.

0: TIM20 clock disabled

1: TIM20 clock enabled

Bit 19 Reserved, must be kept at reset value.

Bit 18 TIM17EN: TIM17 timer clock enable

Set and cleared by software.

0: TIM17 timer clock disabled

1: TIM17 timer clock enabled

Bit 17 TIM16EN: TIM16 timer clock enable

Set and cleared by software.

0: TIM16 timer clock disabled

1: TIM16 timer clock enabled

Bit 16 TIM15EN: TIM15 timer clock enable

Set and cleared by software.

0: TIM15 timer clock disabled

1: TIM15 timer clock enabled

Loading...

Loading...