The STM32 Cortex-M4 instruction set PM0214

54/262 PM0214 Rev 9

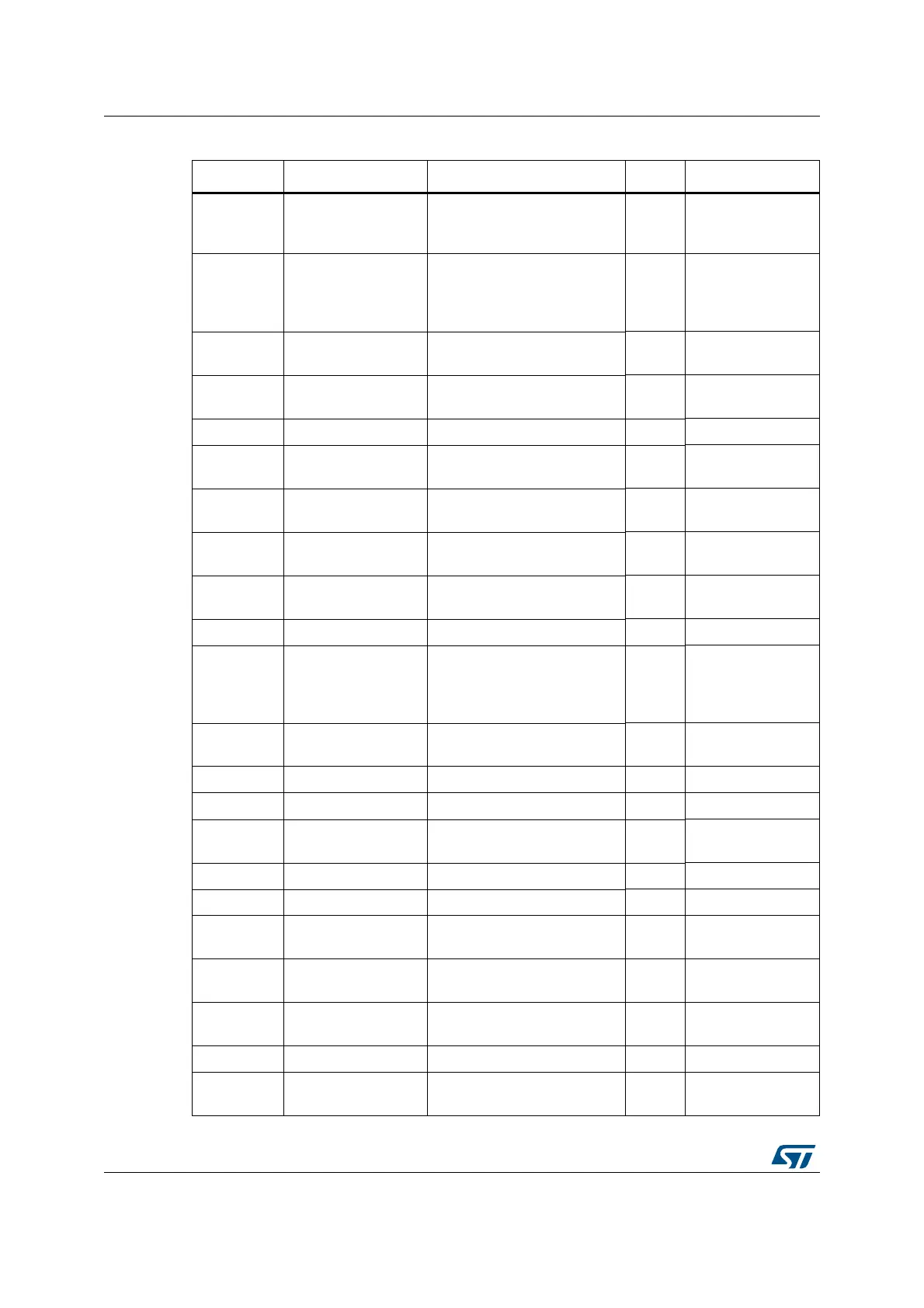

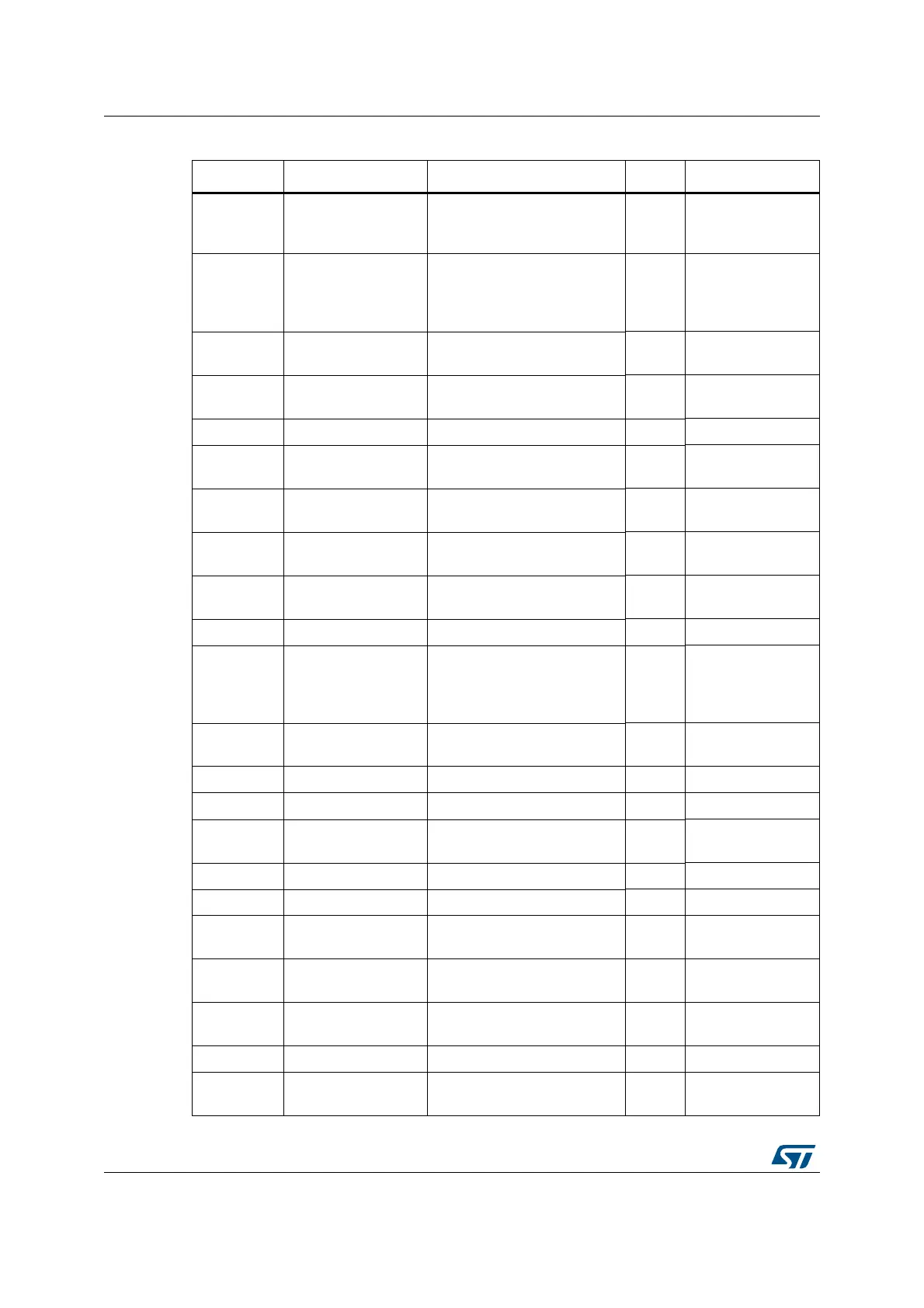

SMLAL RdLo, RdHi, Rn, Rm

Signed multiply with

accumulate (32 x 32 + 64), 64-

bit result

— 3.6.2 on page 111

SMLALBB,

SMLALBT,

SMLALTB,

SMLALTT

RdLo, RdHi, Rn, Rm

Signed multiply accumulate

long,

halfwords

— 3.6.5 on page 115

SMLALD

,

SMLALDX

RdLo, RdHi, Rn, Rm

Signed multiply accumulate

long dual

— 3.6.5 on page 115

SMLAWB,

SMLAWT

Rd, Rn, Rm, Ra

Signed multiply accumulate,

word by halfword

Q 3.6.3 on page 112

SMLSD Rd, Rn, Rm, Ra Signed multiply subtract dual Q 3.6.6 on page 117

SMLSLD RdLo, RdHi, Rn, Rm

Signed multiply subtract long

dual

— 3.6.6 on page 117

SMMLA Rd, Rn, Rm, Ra

Signed most significant word

multiply accumulate

— 3.6.7 on page 119

SMMLS

,

SMMLR

Rd, Rn, Rm, Ra

Signed most significant word

multiply subtract

— 3.6.7 on page 119

SMMUL,

SMMULR

{Rd,} Rn, Rm

Signed most significant word

multiply

— 3.6.8 on page 120

SMUAD {Rd,} Rn, Rm Signed dual multiply add Q 3.6.9 on page 121

SMULBB,

SMULBT

SMULTB,

SMULTT

{Rd,} Rn, Rm Signed multiply (halfwords) — 3.6.10 on page 122

SMULL RdLo, RdHi, Rn, Rm

Signed multiply (32 x 32), 64-

bit result

— 3.6.2 on page 111

SSAT Rd, #n, Rm {,shift #s} Signed saturate Q 3.7.1 on page 126

SSAT16 Rd, #n, Rm Signed saturate 16 Q 3.7.2 on page 127

SSAX {Rd,} Rn, Rm

Signed subtract and add with

exchange

GE 3.5.14 on page 98

SSUB16 {Rd,} Rn, Rm Signed subtract 16 — 3.5.13 on page 97

SSUB8 {Rd,} Rn, Rm Signed subtract 8 — 3.5.13 on page 97

STM Rn{!}, reglist

Store multiple registers,

increment after

— 3.4.6 on page 76

STMDB,

STMEA

Rn{!}, reglist

Store multiple registers,

decrement before

— 3.4.6 on page 76

STMFD,

STMIA

Rn{!}, reglist

Store multiple registers,

increment after

— 3.4.6 on page 76

STR Rt, [Rn, #offset] Store register word — 3.4 on page 69

STRB,

STRBT

Rt, [Rn, #offset] Store register byte — 3.4 on page 69

Table 21. Cortex-M4 instructions (continued)

Mnemonic Operands Brief description Flags Page

Loading...

Loading...