PM0214 Rev 9 53/262

PM0214 The STM32 Cortex-M4 instruction set

261

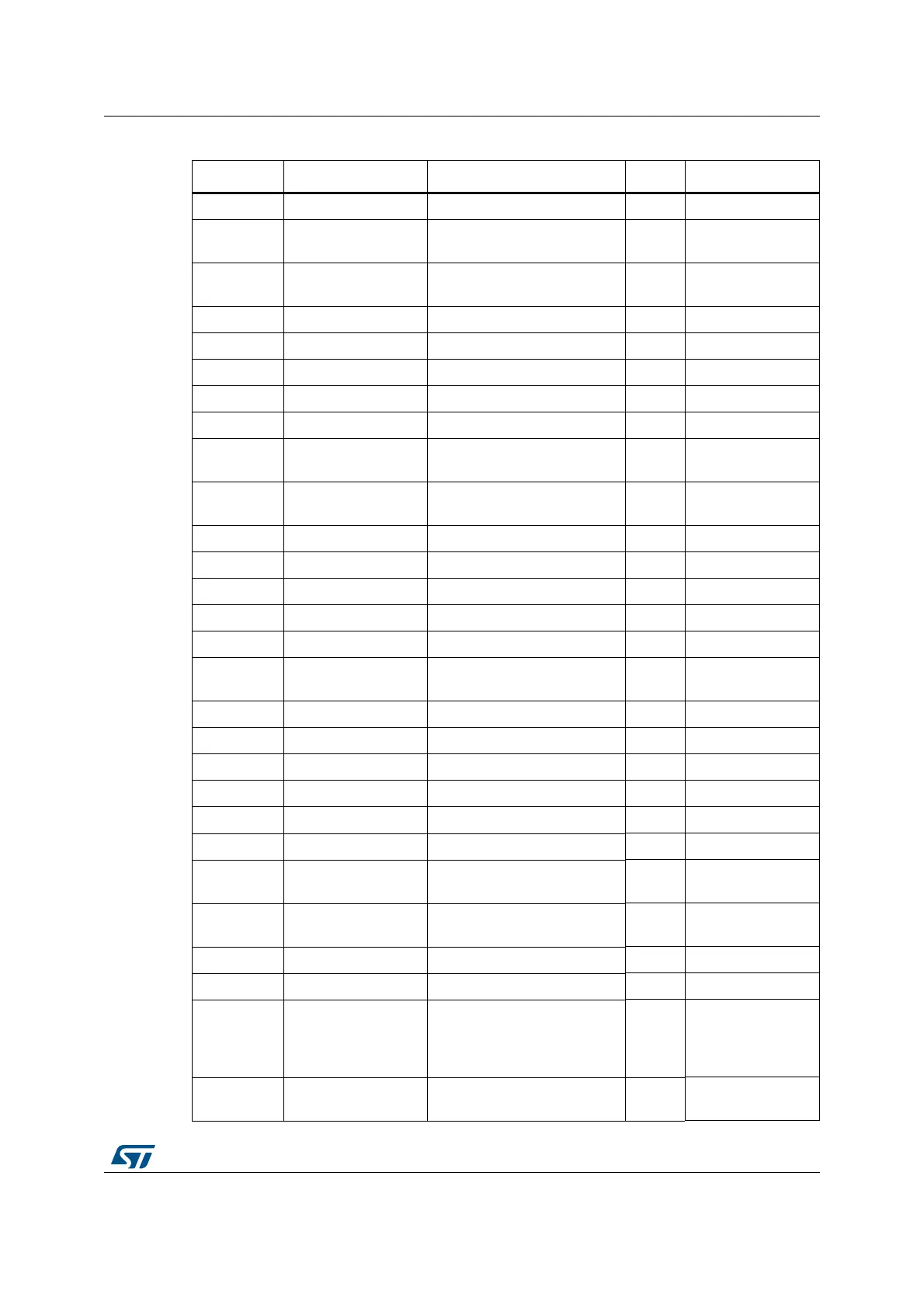

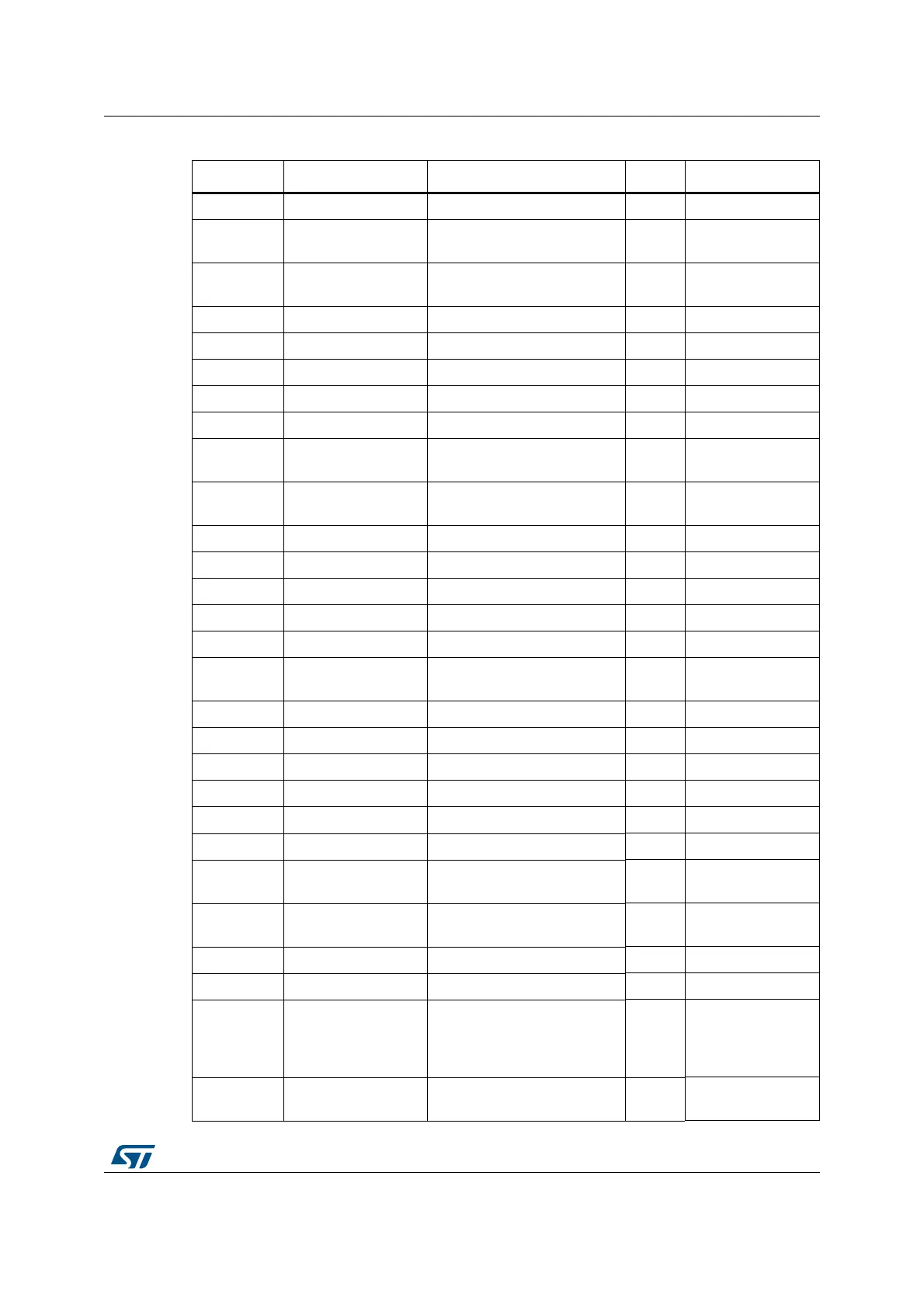

QDADD {Rd,} Rn, Rm Saturating add - 3.7.5 on page 130

QDSUB {Rd,} Rn, Rm

Saturating double and

subtract

- 3.7.5 on page 130

QSAX {Rd,} Rn, Rm

Saturating subtract and add

with exchange

- 3.7.4 on page 129

QSUB {Rd,} Rn, Rm Saturating subtract - 3.7.3 on page 128

QSUB16 {Rd,} Rn, Rm Saturating subtract 16 - 3.7.4 on page 129

QSUB8 {Rd,} Rn, Rm Saturating subtract 8 - 3.7.4 on page 129

RBIT Rd, Rn Reverse bits — 3.7.4 on page 129

REV Rd, Rn Reverse byte order in a word — 3.5.8 on page 92

REV16 Rd, Rn

Reverse byte order in each

halfword

— 3.5.8 on page 92

REVSH Rd, Rn

Reverse byte order in bottom

halfword and sign extend

— 3.5.8 on page 92

ROR, RORS Rd, Rm, <Rs|#n> Rotate right N,Z,C 3.5.3 on page 86

RRX, RRXS Rd, Rm Rotate right with extend N,Z,C 3.5.3 on page 86

RSB, RSBS {Rd,} Rn, Op2 Reverse subtract N,Z,C,V 3.5.1 on page 83

SADD16 {Rd,} Rn, Rm Signed add 16 - 3.5.9 on page 93

SADD8 {Rd,} Rn, Rm Signed add 8 - 3.5.9 on page 93

SASX {Rd,} Rn, Rm

Signed add and subtract with

exchange

- 3.5.14 on page 98

SBC, SBCS {Rd,} Rn, Op2 Subtract with carry N,Z,C,V 3.5.1 on page 83

SBFX Rd, Rn, #lsb, #width Signed bit field extract — 3.9.2 on page 140

SDIV {Rd,} Rn, Rm Signed divide — 3.6.3 on page 112

SEV — Send event — 3.11.9 on page 189

SHADD16 {Rd,} Rn, Rm Signed halving add 16 — 3.5.10 on page 94

SHADD8 {Rd,} Rn, Rm Signed halving add 8 — 3.5.10 on page 94

SHASX {Rd,} Rn, Rm

Signed halving add and

subtract with exchange

— 3.5.11 on page 95

SHSAX {Rd,} Rn, Rm

Signed halving subtract and

add with exchange

— 3.5.11 on page 95

SHSUB16 {Rd,} Rn, Rm Signed halving subtract 16 — 3.5.12 on page 96

SHSUB8 {Rd,} Rn, Rm Signed halving subtract 8 — 3.5.12 on page 96

SMLABB,

SMLABT,

SMLATB,

SMLATT

Rd, Rn, Rm, Ra

Signed multiply accumulate

long

(halfwords)

Q 3.6.3 on page 112

SMLAD

,

SMLADX

Rd, Rn, Rm, Ra

Signed multiply accumulate

dual

Q 3.6.4 on page 114

Table 21. Cortex-M4 instructions (continued)

Mnemonic Operands Brief description Flags Page

Loading...

Loading...