The STM32 Cortex-M4 instruction set PM0214

52/262 PM0214 Rev 9

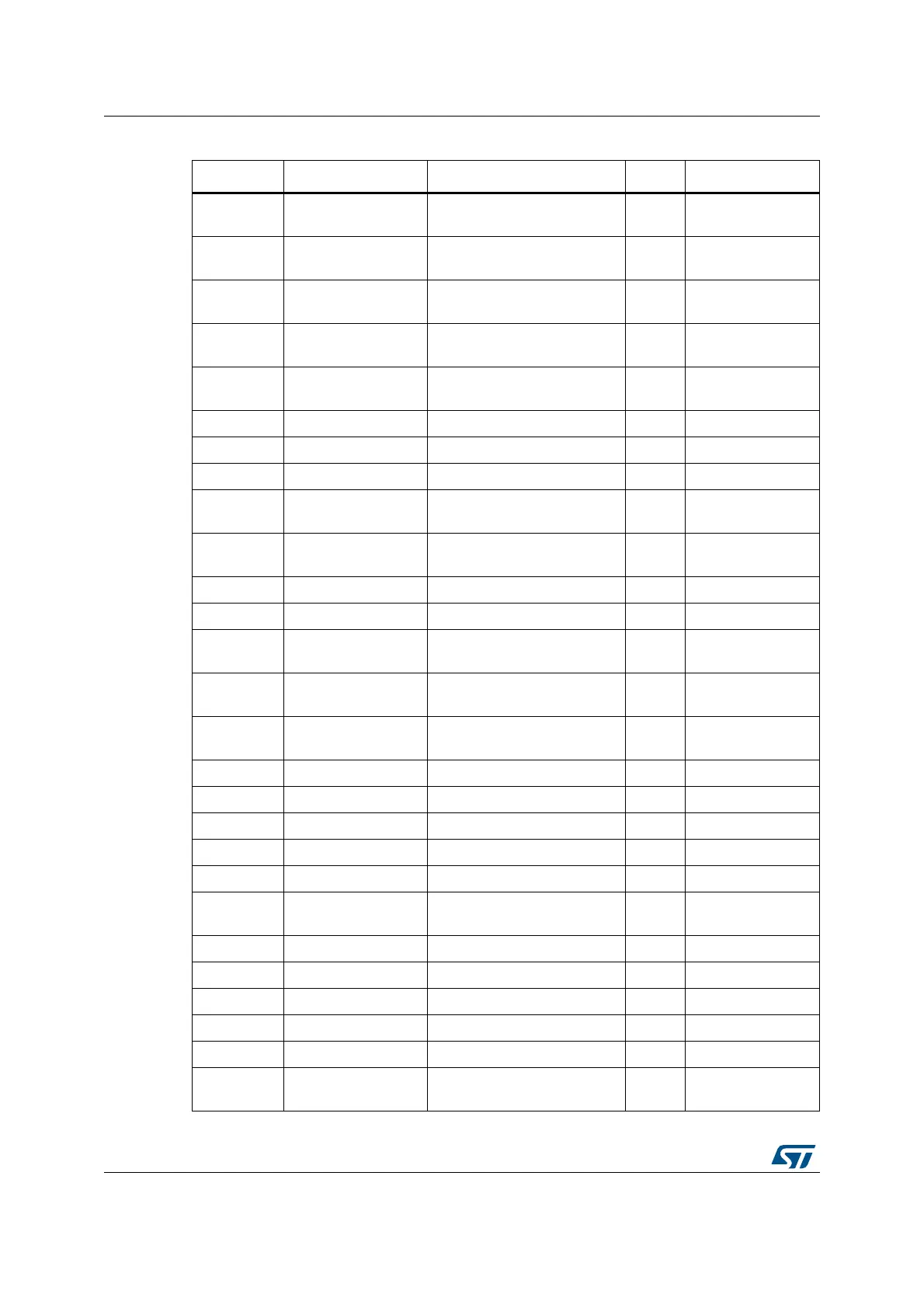

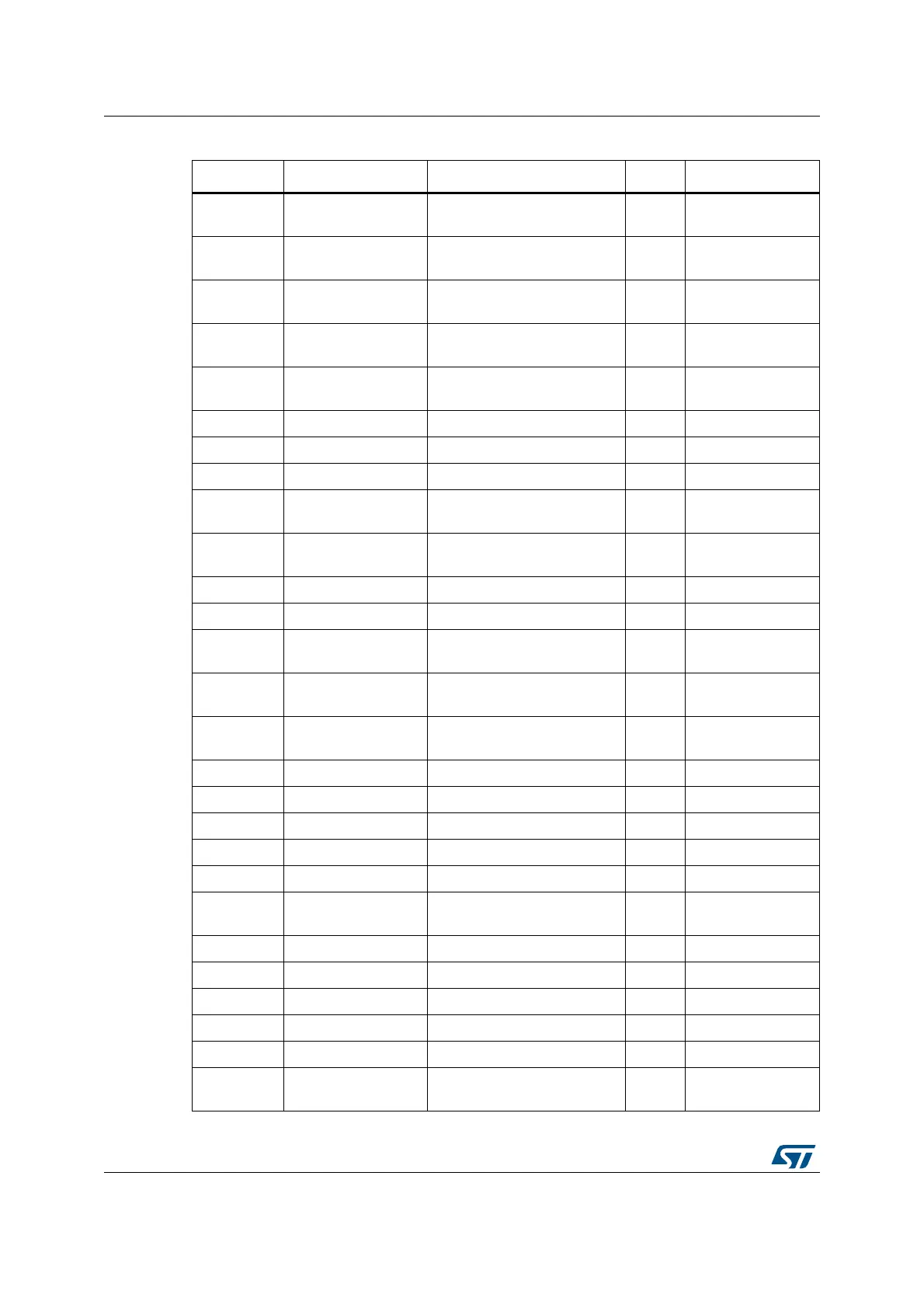

LDREXB Rt, [Rn]

Load register exclusive with

byte

— 3.4.8 on page 79

LDREXH Rt, [Rn]

Load register exclusive with

halfword

— 3.4.8 on page 79

LDRH,

LDRHT

Rt, [Rn, #offset] Load register with halfword — 3.4 on page 69

LDRSB,

LDRSBT

Rt, [Rn, #offset] Load register with signed byte — 3.4 on page 69

LDRSH,

LDRSHT

Rt, [Rn, #offset]

Load register with signed

halfword

— 3.4 on page 69

LDRT Rt, [Rn, #offset] Load register with word — 3.4 on page 69

LSL, LSLS Rd, Rm, <Rs|#n> Logical shift left N,Z,C 3.5.3 on page 86

LSR, LSRS Rd, Rm, <Rs|#n> Logical shift right N,Z,C 3.5.3 on page 86

MLA Rd, Rn, Rm, Ra

Multiply with accumulate, 32-

bit result

— 3.6.1 on page 110

MLS Rd, Rn, Rm, Ra

Multiply and subtract, 32-bit

result

— 3.6.1 on page 110

MOV, MOVS Rd, Op2 Move N,Z,C 3.5.6 on page 89

MOVT Rd, #imm16 Move top — 3.5.7 on page 91

MOVW,

MOV

Rd, #imm16 Move 16-bit constant N,Z,C 3.5.6 on page 89

MRS Rd, spec_reg

Move from special register to

general register

— 3.11.6 on page 186

MSR spec_reg, Rm

Move from general register to

special register

N,Z,C,V 3.11.7 on page 187

MUL, MULS {Rd,} Rn, Rm Multiply, 32-bit result N,Z 3.6.1 on page 110

MVN, MVNS Rd, Op2 Move NOT N,Z,C 3.5.6 on page 89

NOP — No operation — 3.11.8 on page 188

ORN, ORNS {Rd,} Rn, Op2 Logical OR NOT N,Z,C 3.5.2 on page 85

ORR, ORRS {Rd,} Rn, Op2 Logical OR N,Z,C 3.5.2 on page 85

PKHTB,

PKHBT

{Rd,} Rn, Rm, Op2 Pack Halfword - 3.8.1 on page 135

POP reglist Pop registers from stack — 3.4.7 on page 78

PUSH reglist Push registers onto stack — 3.4.7 on page 78

QADD {Rd,} Rn, Rm Saturating double and add - 3.7.3 on page 128

QADD16 {Rd,} Rn, Rm Saturating add 16 - 3.7.3 on page 128

QADD8 {Rd,} Rn, Rm Saturating add 8 - 3.7.3 on page 128

QASX {Rd,} Rn, Rm

Saturating add and subtract

with exchange

- 3.7.4 on page 129

Table 21. Cortex-M4 instructions (continued)

Mnemonic Operands Brief description Flags Page

Loading...

Loading...