PM0214 Rev 9 51/262

PM0214 The STM32 Cortex-M4 instruction set

261

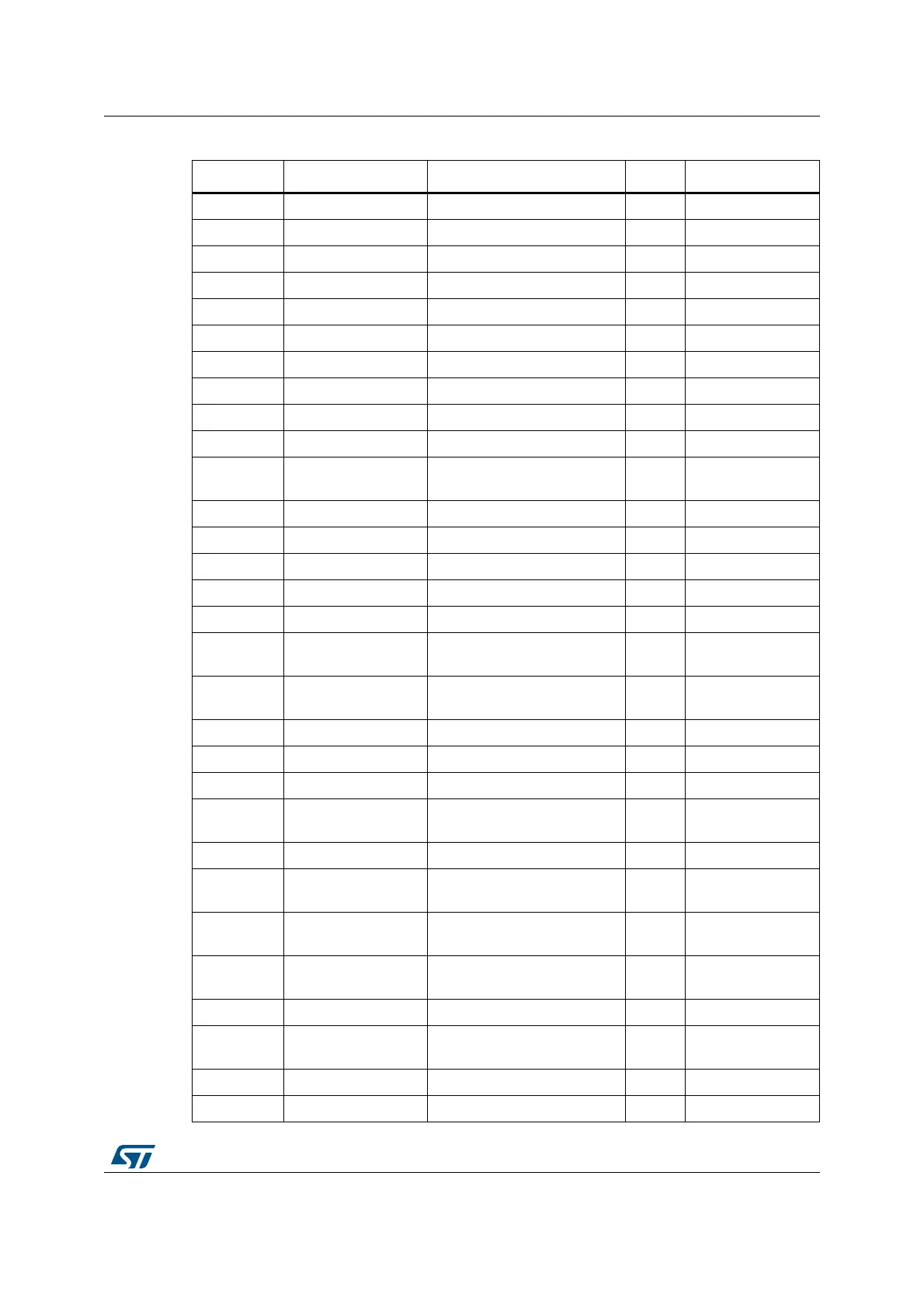

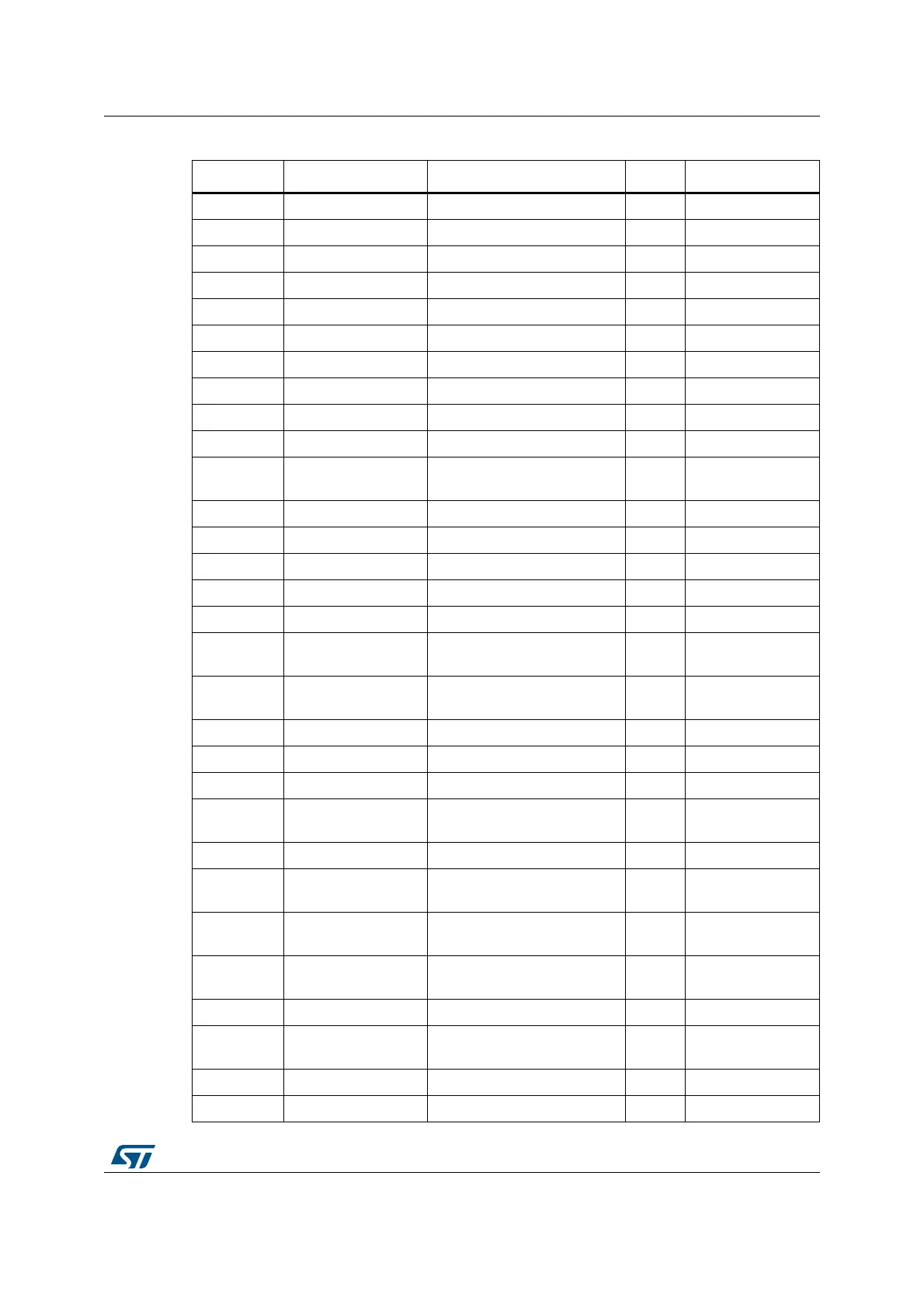

AND, ANDS {Rd,} Rn, Op2 Logical AND N,Z,C 3.5.2 on page 85

ASR, ASRS Rd, Rm, <Rs|#n> Arithmetic shift right N,Z,C 3.5.3 on page 86

B label Branch — 3.9.5 on page 142

BFC Rd, #lsb, #width Bit field clear — 3.9.1 on page 139

BFI Rd, Rn, #lsb, #width Bit field insert — 3.9.1 on page 139

BIC, BICS

{Rd,}

Rn, Op2

Bit clear N,Z,C 3.5.2 on page 85

BKPT #imm Breakpoint — 3.11.1 on page 181

BL label Branch with link — 3.9.5 on page 142

BLX Rm Branch indirect with link — 3.9.5 on page 142

BX Rm Branch indirect — 3.9.5 on page 142

CBNZ Rn, label

Compare and branch if non

zero

— 3.9.6 on page 144

CBZ Rn, label Compare and branch if zero — 3.9.6 on page 144

CLREX — Clear exclusive — 3.4.9 on page 80

CLZ Rd, Rm Count leading zeros — 3.5.4 on page 87

CMN Rn, Op2 Compare negative N,Z,C,V 3.5.5 on page 88

CMP Rn, Op2 Compare N,Z,C,V 3.5.5 on page 88

CPSID iflags

Change processor state,

disable interrupts

— 3.11.2 on page 182

CPSIE iflags

Change processor state,

enable interrupts

— 3.11.2 on page 182

DMB — Data memory barrier — 3.11.4 on page 184

DSB — Data synchronization barrier — 3.11.4 on page 184

EOR, EORS {Rd,} Rn, Op2 Exclusive OR N,Z,C 3.5.2 on page 85

ISB —

Instruction synchronization

barrier

— 3.11.5 on page 185

IT — If-then condition block — 3.9.7 on page 145

LDM Rn{!}, reglist

Load multiple registers,

increment after

— 3.4.6 on page 76

LDMDB,

LDMEA

Rn{!}, reglist

Load multiple registers,

decrement before

— 3.4.6 on page 76

LDMFD,

LDMIA

Rn{!}, reglist

Load multiple registers,

increment after

— 3.4.6 on page 76

LDR Rt, [Rn, #offset] Load register with word — 3.4 on page 69

LDRB,

LDRBT

Rt, [Rn, #offset] Load register with byte — 3.4 on page 69

LDRD Rt, Rt2, [Rn, #offset] Load register with two bytes — 3.4.2 on page 71

LDREX Rt, [Rn, #offset] Load register exclusive — 3.4.8 on page 79

Table 21. Cortex-M4 instructions (continued)

Mnemonic Operands Brief description Flags Page

Loading...

Loading...