Sun Microelectronics

134

UltraSPARC User’s Manual

The sequence is the same for any valid states in Processors 2 and 3.

If no processor has the block, the SC does not generate any S_INV_REQ.

7.16.7 ReadToDiscard Any Block

Condition: Noncacheable read on Processor 1; another processor (P2) owns the

block.

7.16.8 Victim Writeback

Condition: Load or store miss on dirty victim block. SC services read before

Writeback.

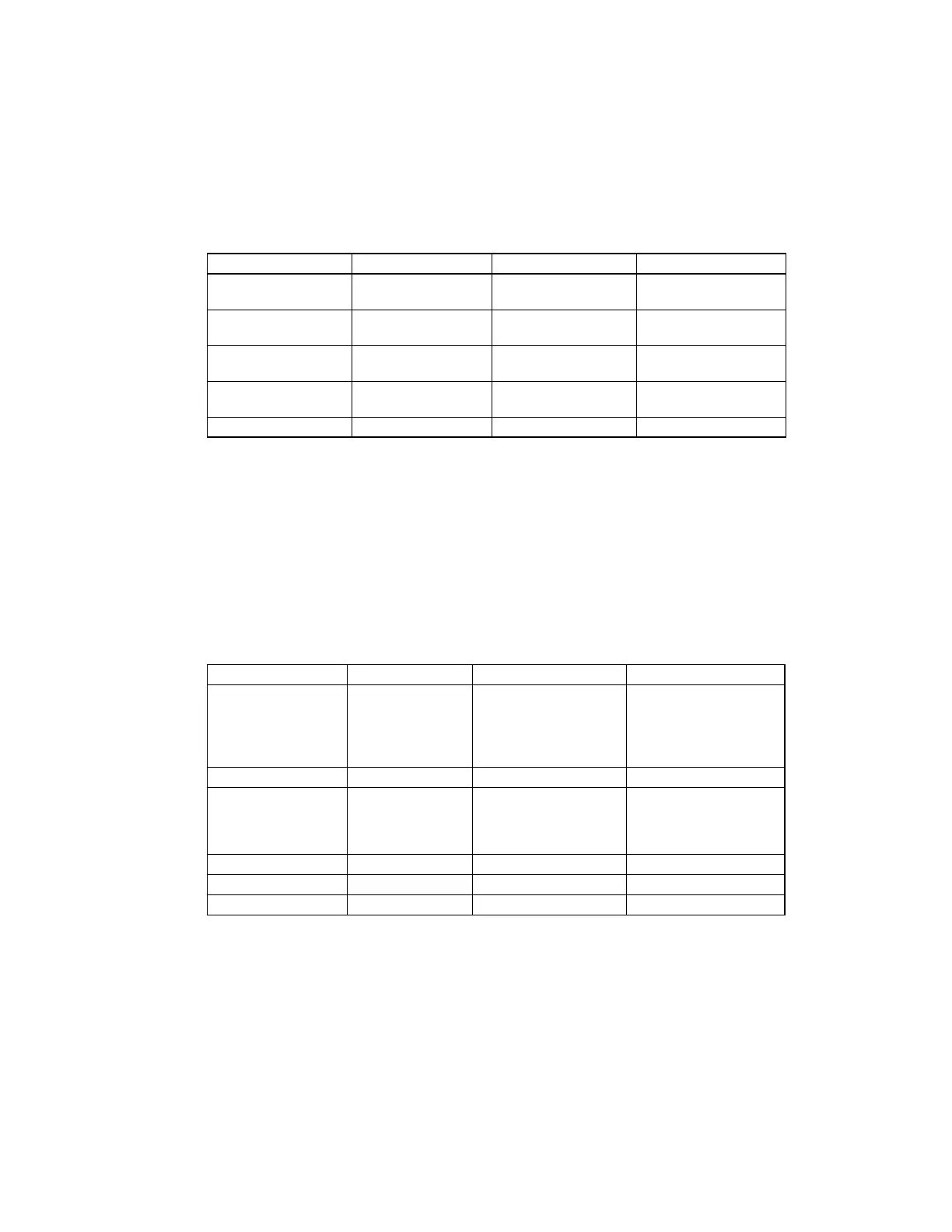

Table 7-30 ReadToOwn for Write Permission

Processor 1 System Processor 2 Processor 3

Initial state: Etag{S}

P_RDO_REQ to System

Initial state: Etag{O} Initial state:Etag{S}

S_INV_REQ to P2

S_INV_REQ to P3

P2 updates Etag{O → I}

P_SACK to System

P3 updates Etag{S → I}

P_SACK to System

S_OAK to P1

(no data is transferred)

P1 updates Etag{S → M} Final state: Etag{I} Final state: Dtag{I}

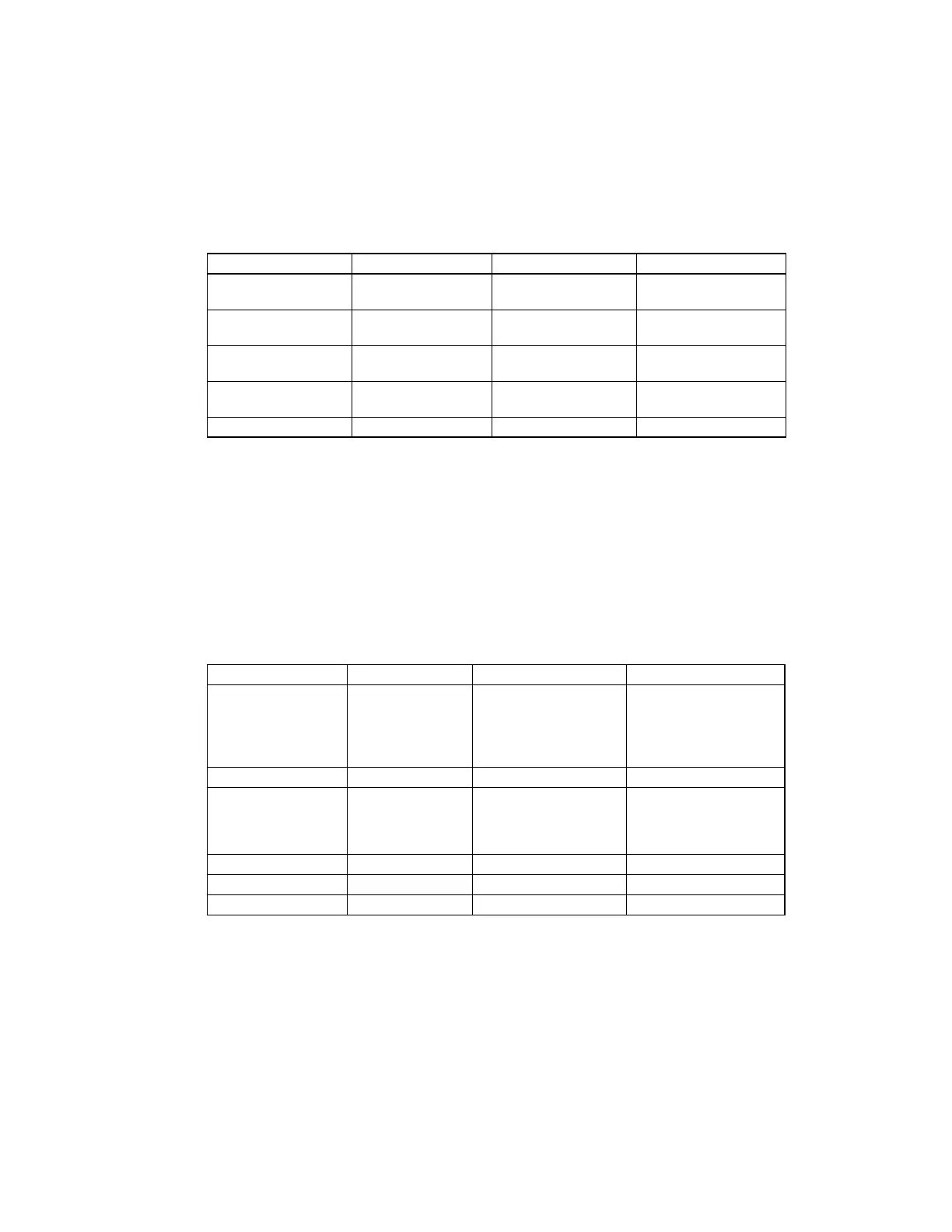

Table 7-31 ReadToDIscard

Processor 1 System Processor 2 Processor 3

Initial state: Etag{I}

P_RDD_REQ to System

Initial state:

Etag{M} or

Etag{O} or

Etag{E}

Initial state:

Etag{I}

S_CPD_REQ to P2

P2 copies block to copy-

back buffer

P_SACK reply to System

S_CRAB reply to P2

S_RBS reply to P1

Final state: No change Final state: No change Final state: No change

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...