Sun Microelectronics

135

7. UltraSPARC External Interfaces

The following transaction sequence is the same as for Section 7.16.1, “Read-

ToShare Block,” except that the miss generates a dirty victim block. UltraSPARC

always issues the read request before the Writeback request, but the requests can

be completed in any order. In this example, the read completes first. The follow-

ing section shows the sequence when the Writeback completes first.

7.16.9 Victim Writeback Serviced Before Read

Condition: Load/store miss on dirty victim block. SC services Writeback before

read.

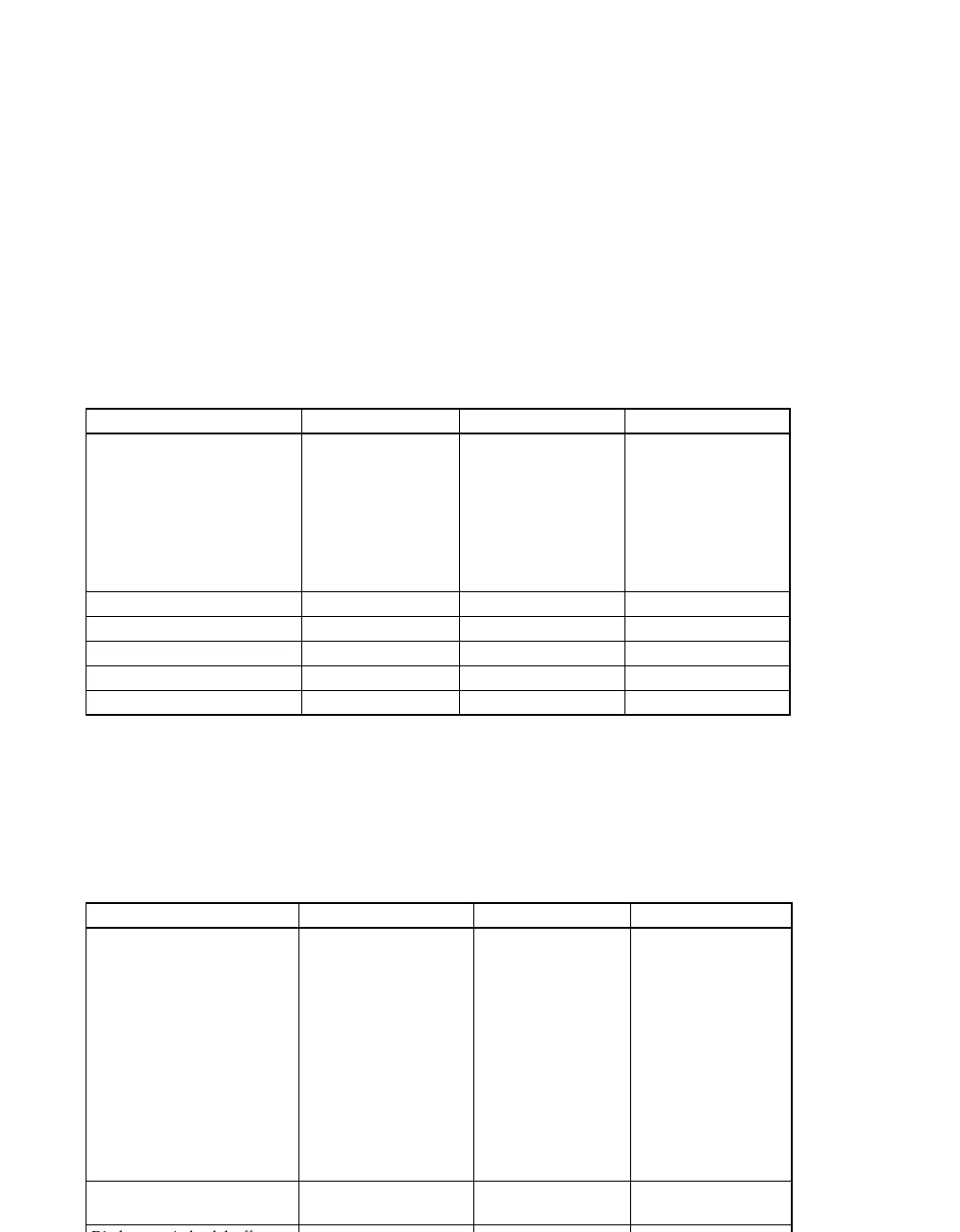

Table 7-32 Victim Writeback, Read Miss Serviced Before Writeback

Processor 1 System Processor 2 Processor 3

Initial victim state:

Etag1{M},

Initial missed state:

Etag2{I}

P1 copies the victim block into

the Writeback buffer

P_RDS_REQ to System

(DVP bit set)

Initial state:

Etag2{I}

Initial state:

Etag2{I}

S_RBU reply to P1

P1 updates Etag2{I → E}

P_WRB_REQ to System

S_WAB reply to P1

P1 clears Writeback buffer tag Final state: No change Final state: No change

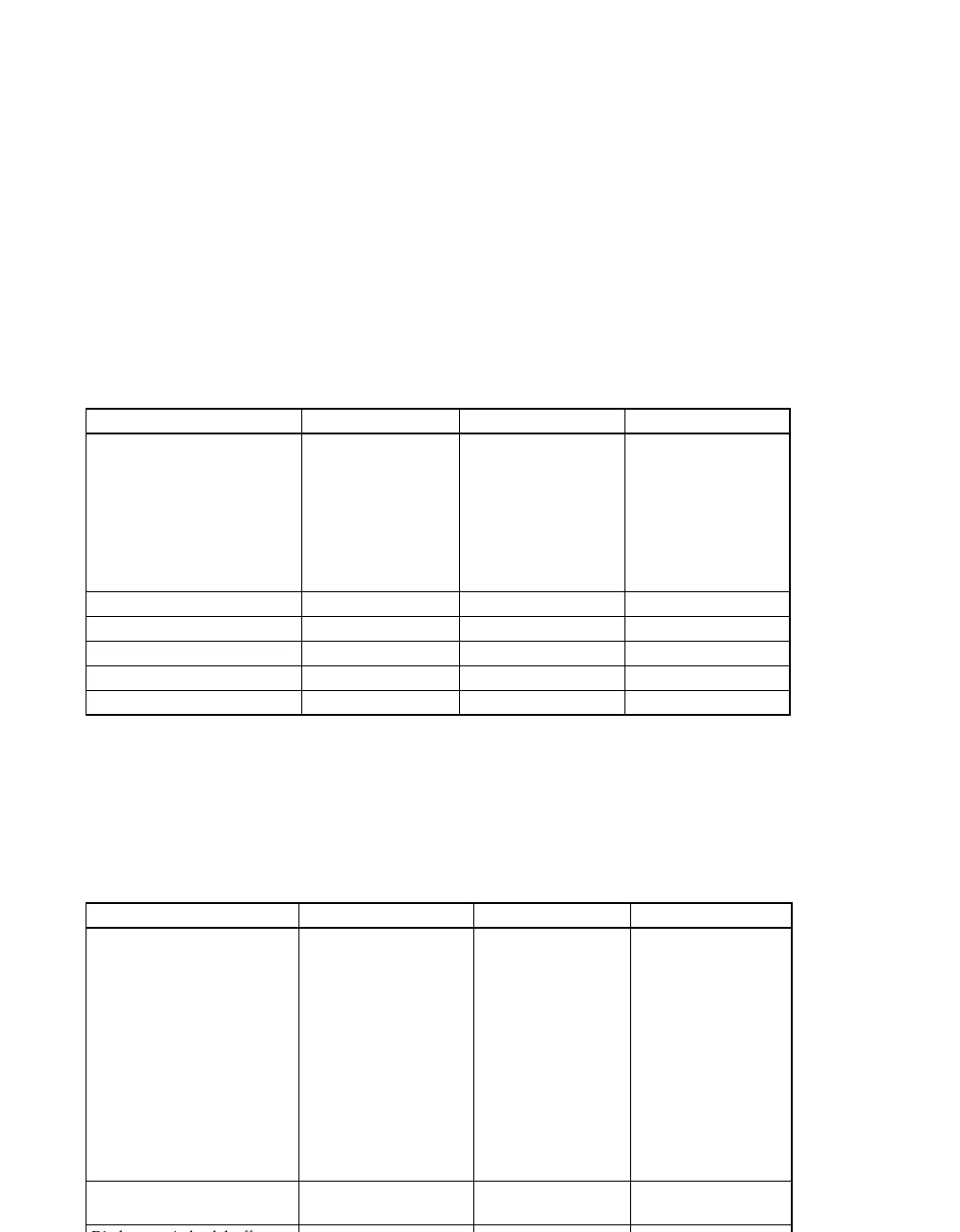

Table 7-33 Victim Writeback: Writeback Serviced Before Read Miss

Processor 1 System Processor 2 Processor 3

Initial victim state:

Etag1{M}

Initial missed state:

Etag2{I}

P1 copies the victim block

into the writeback buffer

P_RDS_REQ to System

(DVP bit set)

P_WRB_REQ to System

Initial state:

Etag2{I}

Initial state:

Etag2{I}

S_WAB reply to P1

Start write to memory

P1 clears writeback buffer tag

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...