Sun Microelectronics

181

11. Error Handling

• Bits <19:16> and <15:0> contain the tag and data parity syndromes

respectively. Syndrome bits are endian-neutral, that is, bit 0 corresponds to

bits<7:0> of the E-Cache data bus (that is, bytes whose least significant four

address bits are F

16

). The syndrome fields have the status of the first

occurrence of the highest priority error related to that field. If no status bit is

set corresponding to that field, the contents of the syndrome field will be zero.

The AFSR must be cleared by software explicitly; it is not cleared automatically

during a read. Writes to the AFSR sticky bits (<32:20>) with particular bits set

will clear the corresponding bits in the AFSR. Bits associated with disrupting

traps must be cleared before reenabling interrupts to prevent multiple traps for

the same error. Writes to the AFSR sticky bits with particular bits clear will not af-

fect the corresponding bits in the AFSR. If software attempts to clear error bits at

the same time as an error occurs, the clear will be performed before logging the

new error status. The syndrome field is read only and writes to this field are ig-

nored.

Refer to Table 10-1, “Machine State After Reset and in RED_state,” on page 172

for the state of this register after reset.

Name: ASI_ASYNC_FAULT_STATUS

ASI=4C

16

, VA<63:0>=0

16

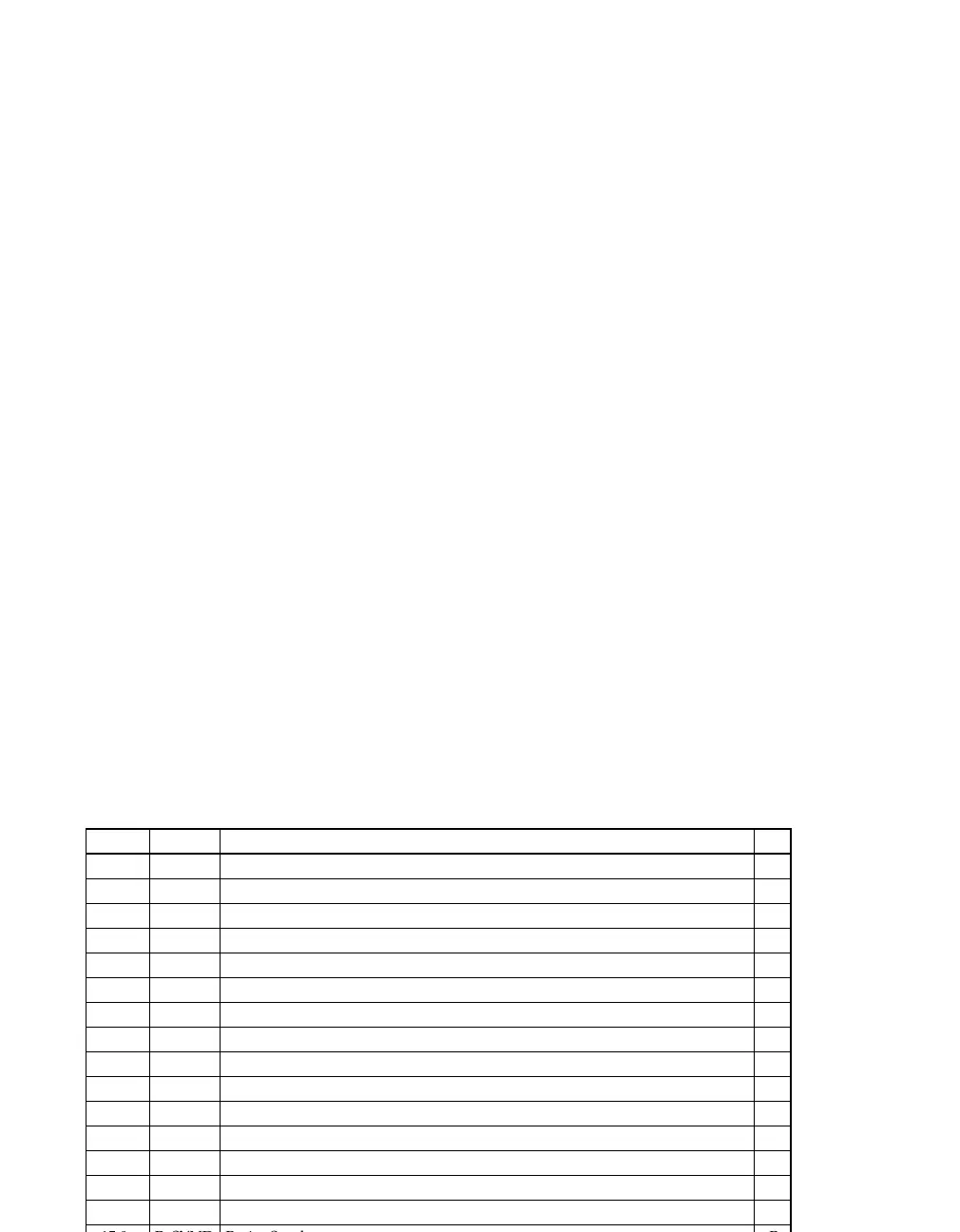

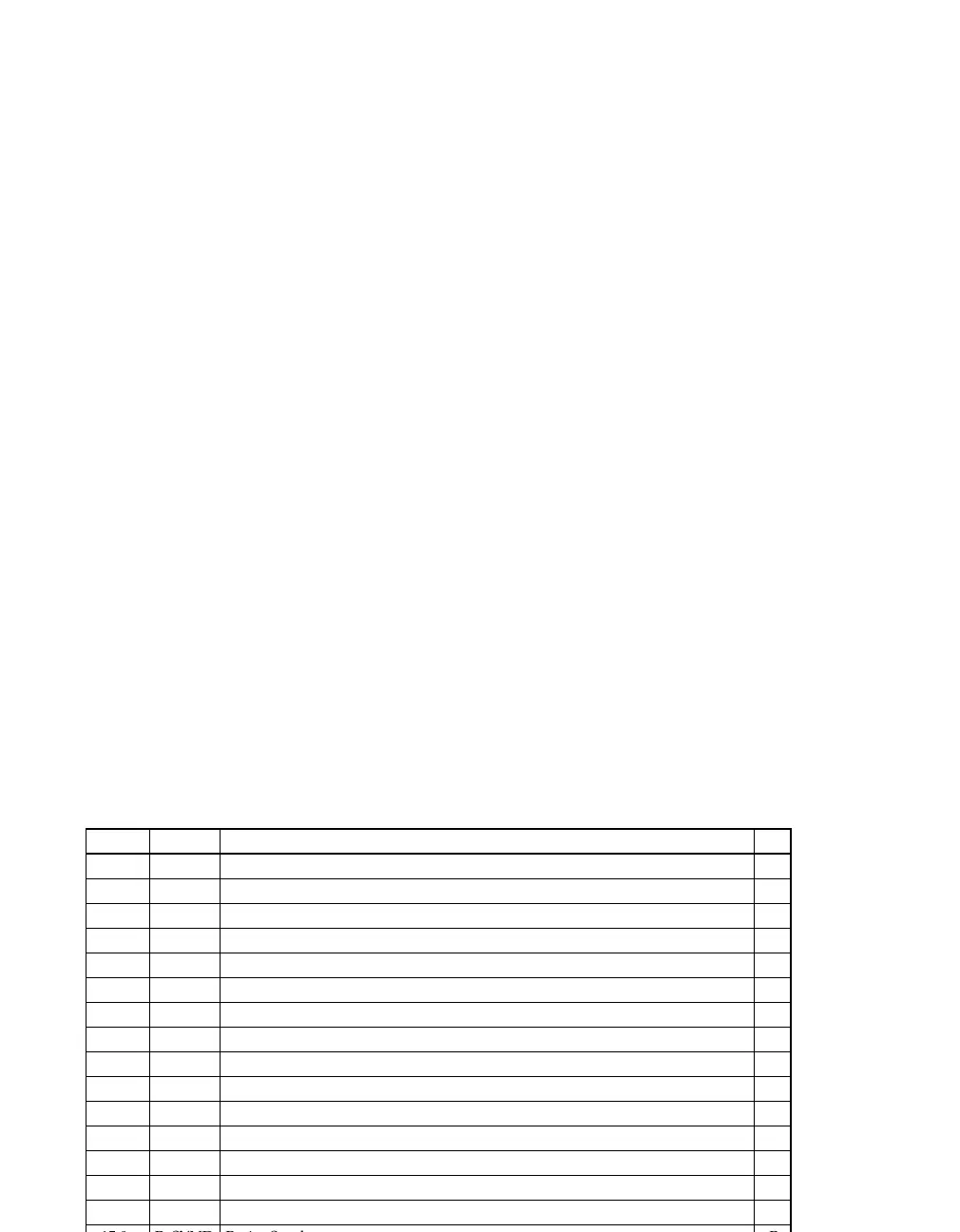

Table 11-2 Asynchronous Fault Status Register

Bits Field Use RW

<63:33> Reserved —R

<32> ME Multiple Error of same type occurred RW

<31> PRIV Privileged code access error(s) has occurred RW

<30> ISAP System Address Parity error on incoming address RW

<29> ETP Parity error in E-Cache Tag SRAM RW

<28> IVUE Interrupt Vector Uncorrectable error RW

<27> TO Time-Out from system bus RW

<26> BERR Bus Error from system Bus RW

<25> LDP Data Parity error from UDB-generated data (noncacheable access or cache fill) RW

<24> CP Copy-out (intervention) Parity error RW

<23> WP Data parity error from E-Cache SRAMs for Write-back (victim) RW

<22> EDP Data parity error from E-Cache SRAMs RW

<21> UE Uncorrectable ECC error (E_SYND in UDB) RW

<20> CE Correctable memory read ECC error (E_SYND in UDB) RW

<19:16> ETS E-Cache Tag parity Syndrome R

<15:0> P_SYND Parity Syndrome R

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...