Sun Microelectronics

182

UltraSPARC User’s Manual

11.3.3 Asynchronous Fault Address Register

This register is valid when one of the Asynchronous Fault Status Register (AFSR)

error status bits that capture address is set (correctable or uncorrectable memory

ECC error, bus time-out or bus error). The address corresponds to the first occur-

rence of the highest priority error in AFSR that captures address (see Section

11.5.1, “AFAR Overwrite Policy,” on page 185). Address capture is reenabled by

clearing all corresponding error bits in AFSR. If software attempts to write to

these bits at the same time as an error that captures address occurs, the error ad-

dress will be stored.

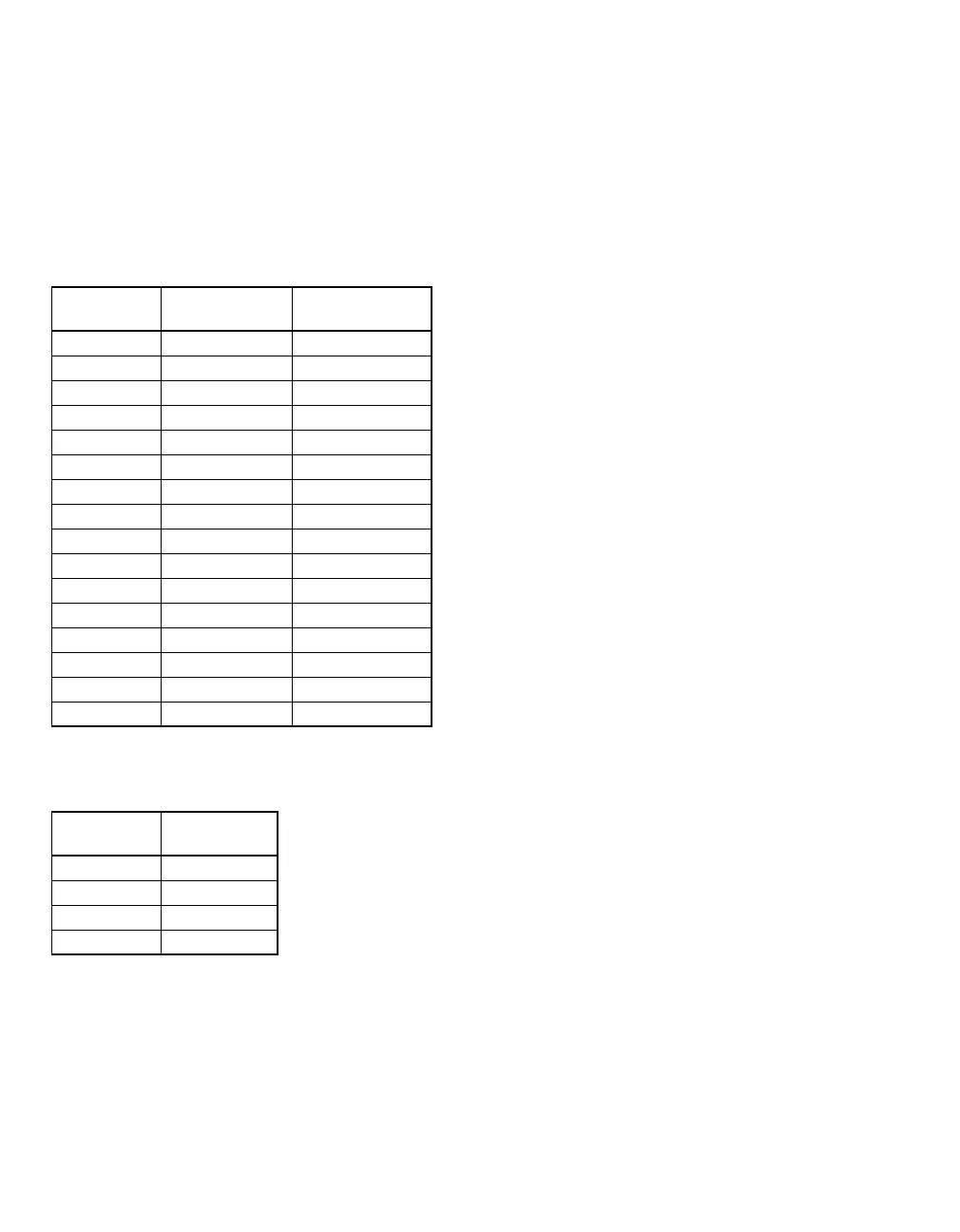

Table 11-3 E-Cache Data Parity Syndrome Bit Orderings

Byte

Address

E- Cache Data

Bus Bits

Syndrome Bit

F

16

<7:0> 0

E

16

<15:8> 1

D

16

<23:16> 2

C

16

<31:24> 3

B

16

<39:32> 4

A

16

<47:40> 5

9

16

<55:48> 6

8

16

<63:56> 7

7

16

<71:64> 8

6

16

<79:72> 9

5

16

<87:80> 10

4

16

<95:88> 11

3

16

<103:96> 12

2

16

<111:104> 13

1

16

<119:112> 14

0

16

<127:120> 15

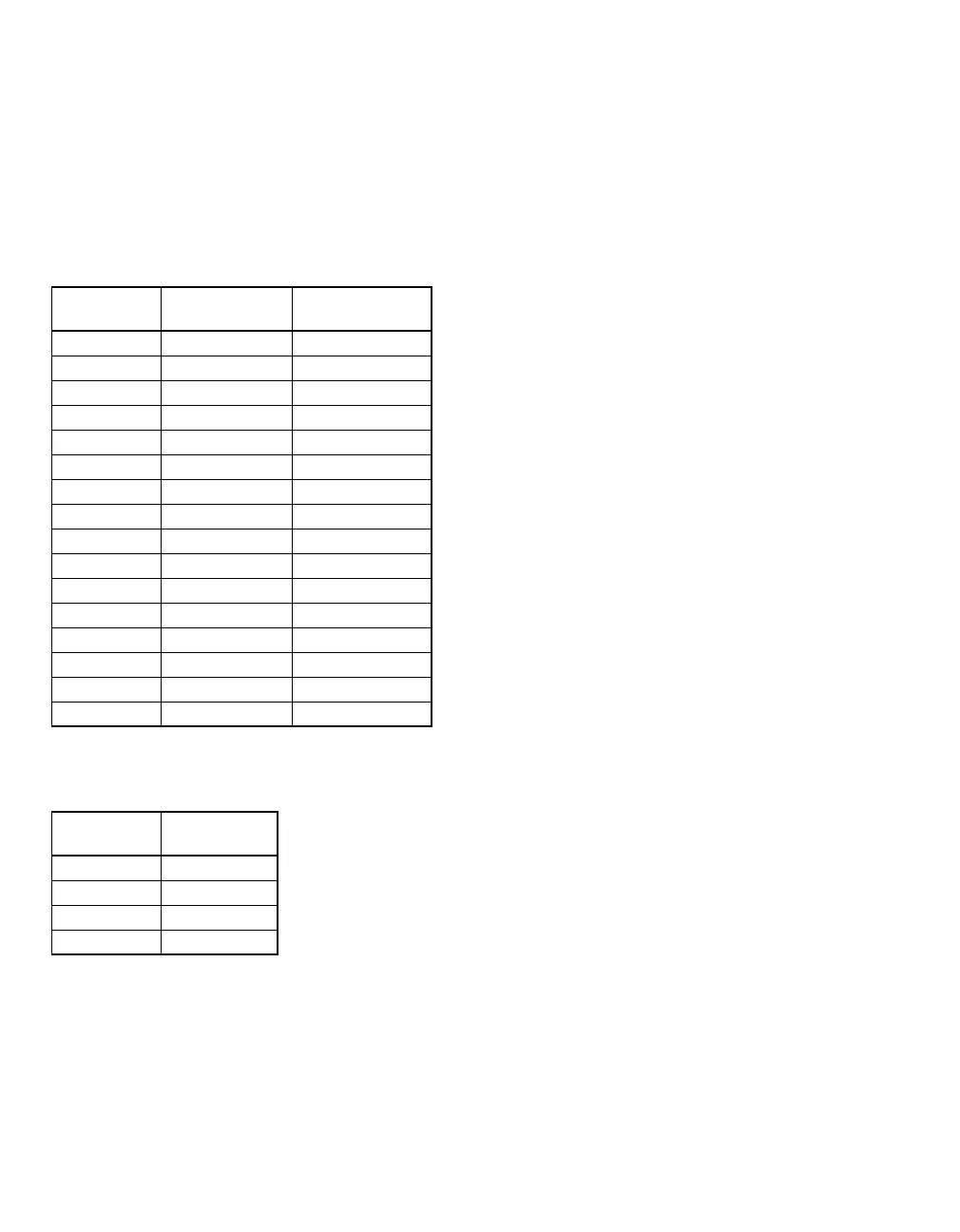

Table 11-4 E-Cache Tag Parity Syndrome Bit Orderings

E-Cache Tag

Bus Bits

Syndrome Bit

<7:0> 0

<15:8> 1

<21:16> 2

<24:22> 3

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...