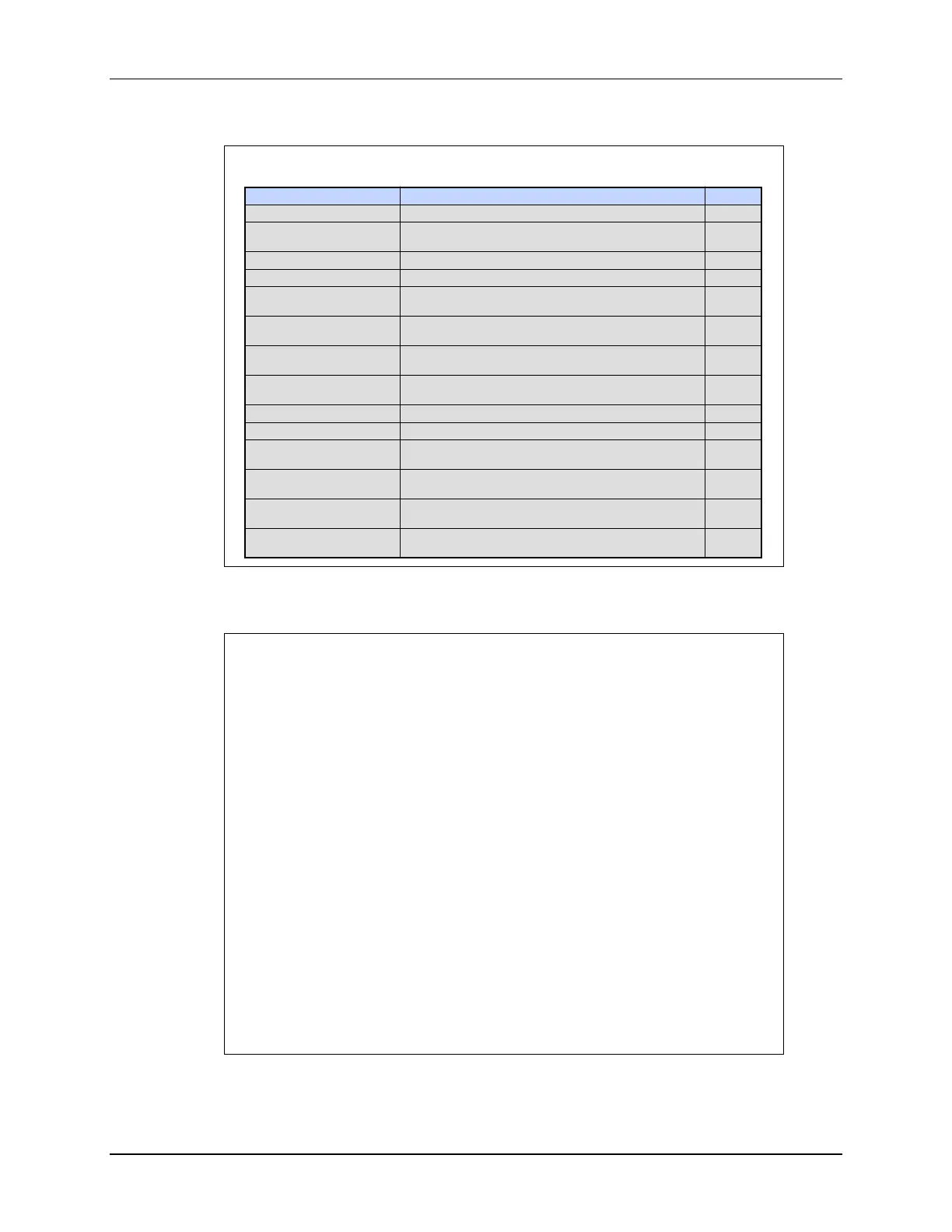

Complex Math Instructions

Complex Math Operation Example Instruction Cycles

Negative

VNEG VRa

1

Setup Shift Value

Left and Right

VSETSHR #5bit

VSETSHL #5bit

1

Saturation On/Off

VSATON / VSATOFF

1

Rounding On/Off

VRNDON / VRNDOFF

1

Clear Overflow Flag

Real & Imaginary

VCLROVFR

VCLROVFI

1

32+32=32-bit

Add or Subtract

VCADD VR5, VR4, VR3, VR2

VCSUB VR5, VR4, VR3, VR2

1

1

16+32=16-bit

Add or Subtract

VCDADD16 VR5, VR4, VR3, VR2

VCDSUB16 VR5, VR4, VR3, VR2

1

1

16x16 = 32-bit

Multiply

VCMPY VR3, VR2, VR1, VR0

2p

Complex MAC

VCMAC VR5, VR4, VR3, VR2, VR1, VR0

2p

RPT || MAC

VCMAC VR7, VR6, VR5, VR4, mem32, XAR7++

2p + N

Add/Sub/Multiply

with Parallel Load

VCADD VR5,VR4,VR3,VR2

||VMOV32 VR2, mem32

1/1

ADD16/SUB16

with Parallel Load

VCSUB16 VR6,VR4,VR3,VR2

||VMOV32 VR2, mem32

1/1

Multiply

with Parallel Store

VCMPY VR3, VR2, VR1, VR0

||VMOV32 mem32, VR2

2p/1

MAC

with Parallel Load

VMAC VR5, VR4, VR3, VR2, VR1, VR0

||VMOV32 VRa, mem32

2p/1

VCU Summary

VCU extends the capability of the C28x

CPU with additional support for:

CRC operations

Viterbi decode

Complex math

Instructions are an extension of the

current instruction set

Targeted towards specific algorithms

Communications and memory robustness

checking

Fast Viterbi decode for communications

Complex filters and FFT

PLC and radar applications

Loading...

Loading...