10–2 Chapter 10: Interrupts

Interrupts for Endpoints

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

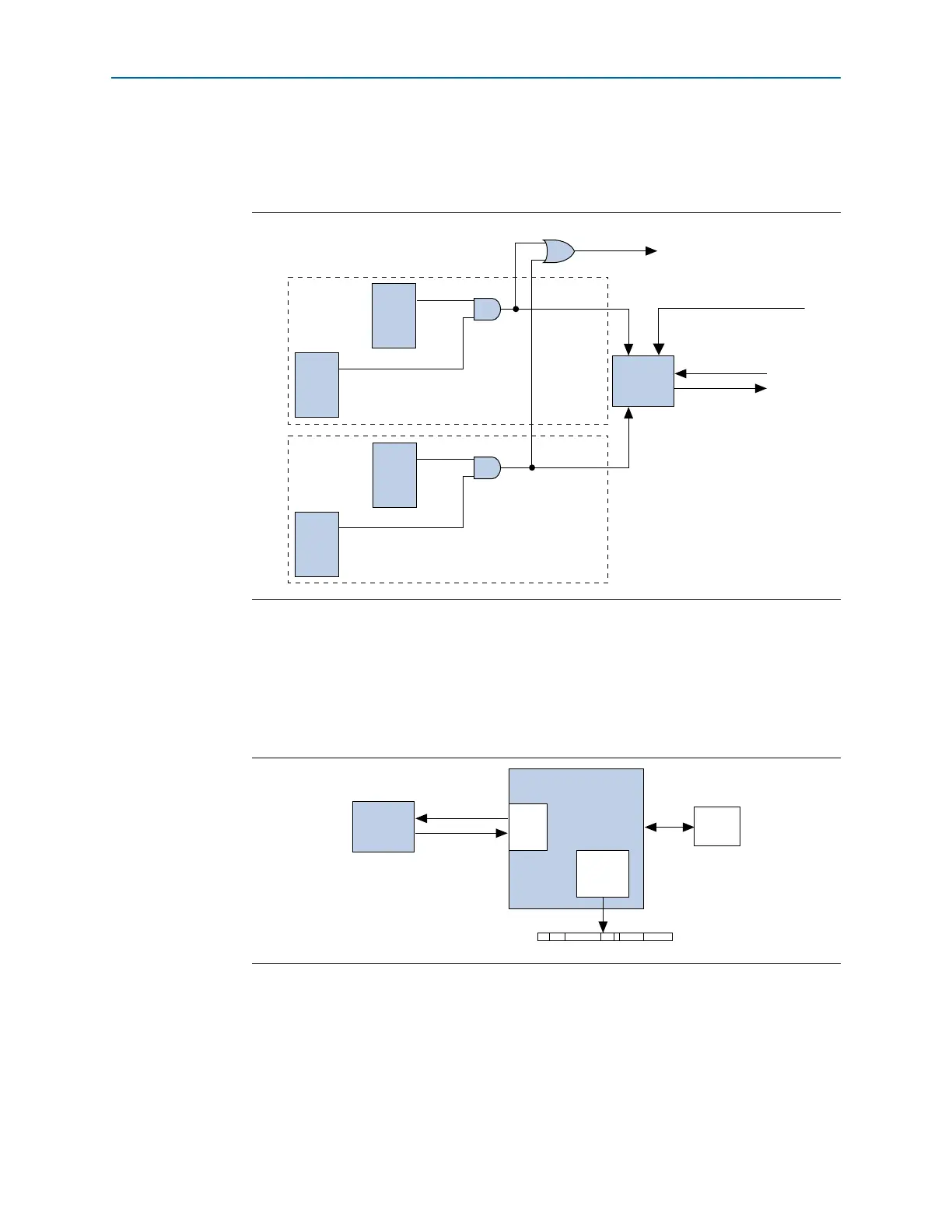

Figure 10–2 illustrates a possible implementation of the MSI handler block with a per

vector enable bit. A global Application Layer interrupt enable can also be

implemented instead of this per vector MSI.

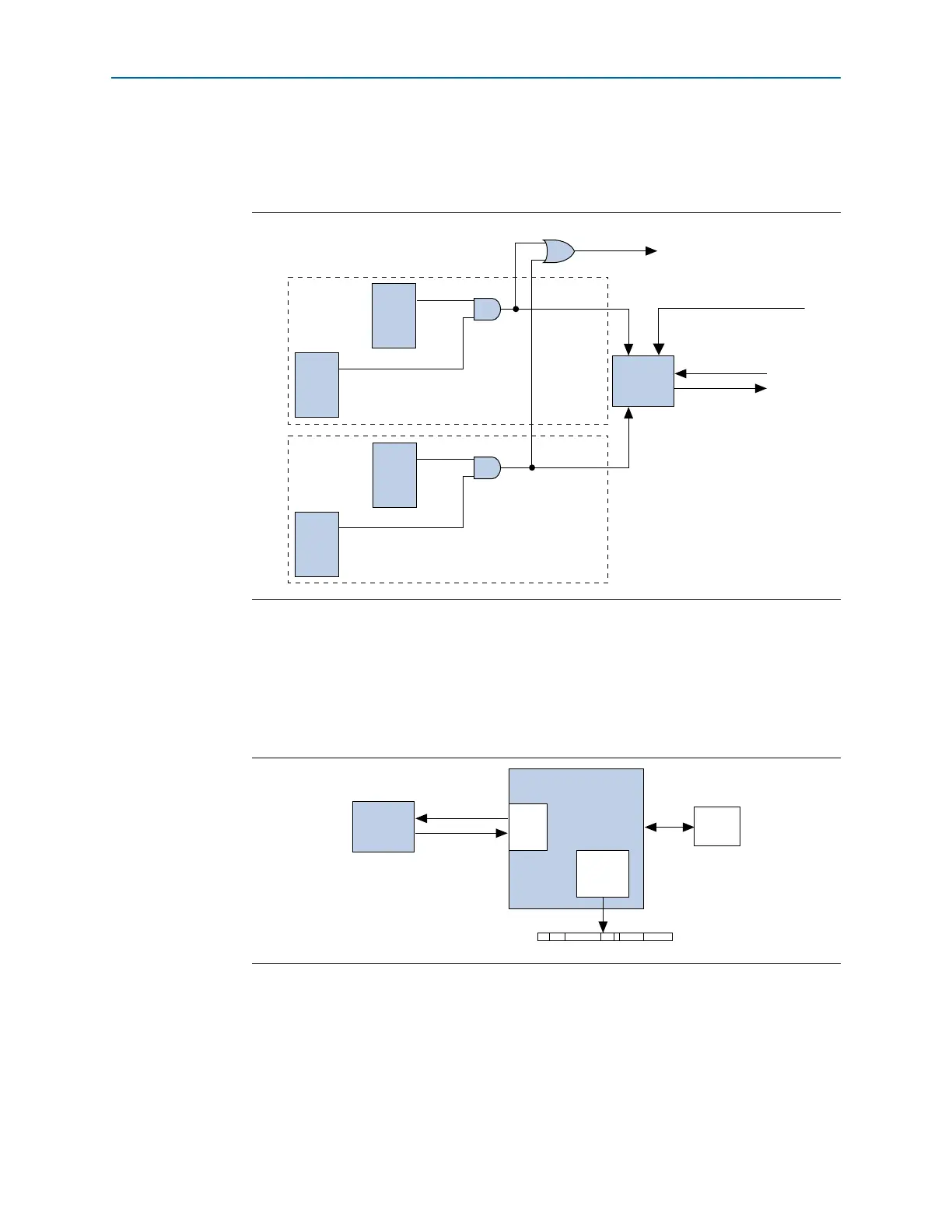

There are 32 possible MSI messages. The number of messages requested by a

particular component does not necessarily correspond to the number of messages

allocated. For example, in Figure 10–3, the Endpoint requests eight MSIs but is only

allocated two. In this case, you must design the Application Layer to use only two

allocated messages.

Figure 10–2. Example Implementation of the MSI Handler Block

Figure 10–3. MSI Request Example

app_int_en0

app_int_sts0

app_msi_req0

app_int_en1

app_int_sts1

app_msi_req1

app_int_sts

MSI

Arbitration

msi_enable & Master Enable

app_msi_req

app_msi_ack

Vector 1

Vector 0

R/W

R/W

Endpoint

8 Requested

2 Allocated

Root Complex

CPU

Interrupt Register

Root

Port

Interrupt

Block

Loading...

Loading...