3–10 Chapter 3: Parameter Settings

Port Functions

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

Link

Table 3–12 describes the Link Capabilities register parameters.

MSI

Table 3–12 describes the MSI Capabilities register parameters.

MSI-X

Table 3–12 describes the MSI-X Capabilities register parameters.

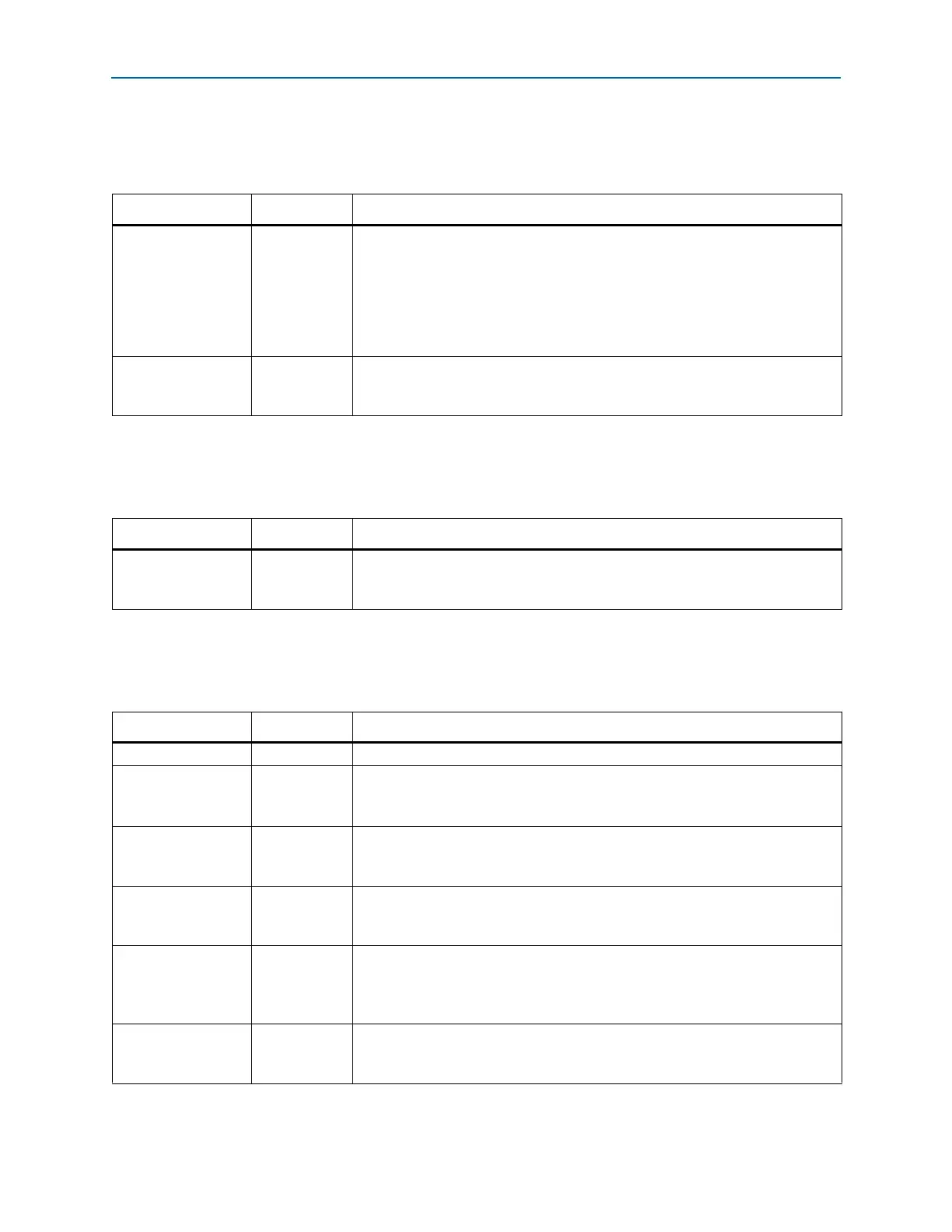

Table 3–11. Link 0x090

Parameter Value Description

Data link layer active

reporting

On/Off

Turn On this option for a downstream port, if the component supports the optional

capability of reporting the DL_Active state of the Data Link Control and

Management State Machine. For a hot-plug capable downstream port (as

indicated by the

Hot-Plug Capable

field of the

Slot

Capabilities

register),

this option must be turned On. For upstream ports and components that do not

support this optional capability, turn Off this option. This parameter is only

supported in Root Port mode.

Surprise down

reporting

On/Off

When this option is On, a downstream port supports the optional capability of

detecting and reporting the surprise down error condition. This parameter is only

supported in Root Port mode.

Table 3–12. MSI and MSI-X Capabilities 0x050–0x05C,

Parameter Value Description

MSI messages

requested

1, 2, 4,

8, 16

Specifies the number of messages the Application Layer can request. Sets the

value of the

Multiple Message Capable

field of the

Message Control

register, 0x050[31:16].

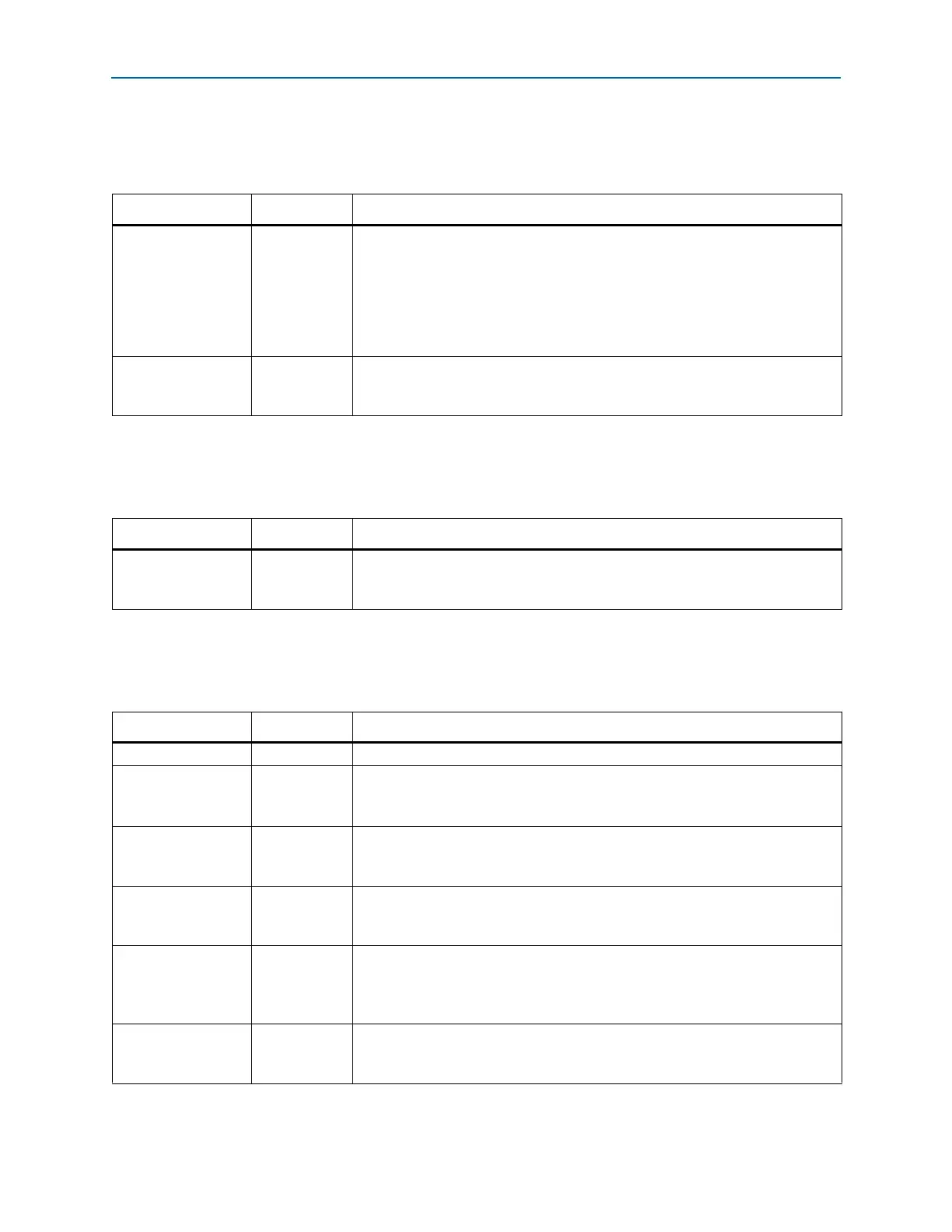

Table 3–13. MSI and MSI-X Capabilities 0x068–0x06C

Parameter Value Description

Implement MSI-X On/Off When On, enables the MSI-X functionality.

Table size

0x068[26:16]

[10:0]

System software reads this field to determine the MSI-X Table size <n>, which is

encoded as <n–1>. For example, a returned value of 2047 indicates a table size of

2048. This field is read-only. Legal range is 0–2047 (2

11

).

Table Offset [31:3]

Points to the base of the MSI-X Table. The lower 3 bits of the table BAR indicator

(BIR) are set to zero by software to form a 32-bit qword-aligned offset. This field is

read-only. Legal range is 0–2

28

.

Table BAR Indicator <5–1>:0

Specifies which one of a function’s BARs, located beginning at 0x10 in

Configuration Space, is used to map the MSI-X table into memory space. This field

is read-only. Legal range is 0–5.

Pending Bit Array

(PBA) Offset

31:3

Used as an offset from the address contained in one of the function’s Base

Address registers to point to the base of the MSI-X PBA. The lower 3 bits of the

PBA BIR are set to zero by software to form a 32-bit qword-aligned offset. This

field is read-only. Legal range is 0–2

28

.

PBA BAR Indicator

(BIR)

<5–1>:0

Indicates which of a function’s Base Address registers, located beginning at 0x10

in Configuration Space, is used to map the function’s MSI-X PBA into memory

space. This field is read-only. Legal range is 0–5.

Loading...

Loading...