4–8 Chapter 4: IP Core Architecture

Protocol Layers

Cyclone V Hard IP for PCI Express November 2011 Altera Corporation

■ Transmitting and decoding the training sequence

■ Providing hardware autonomous speed control

■ Implementing auto lane reversal

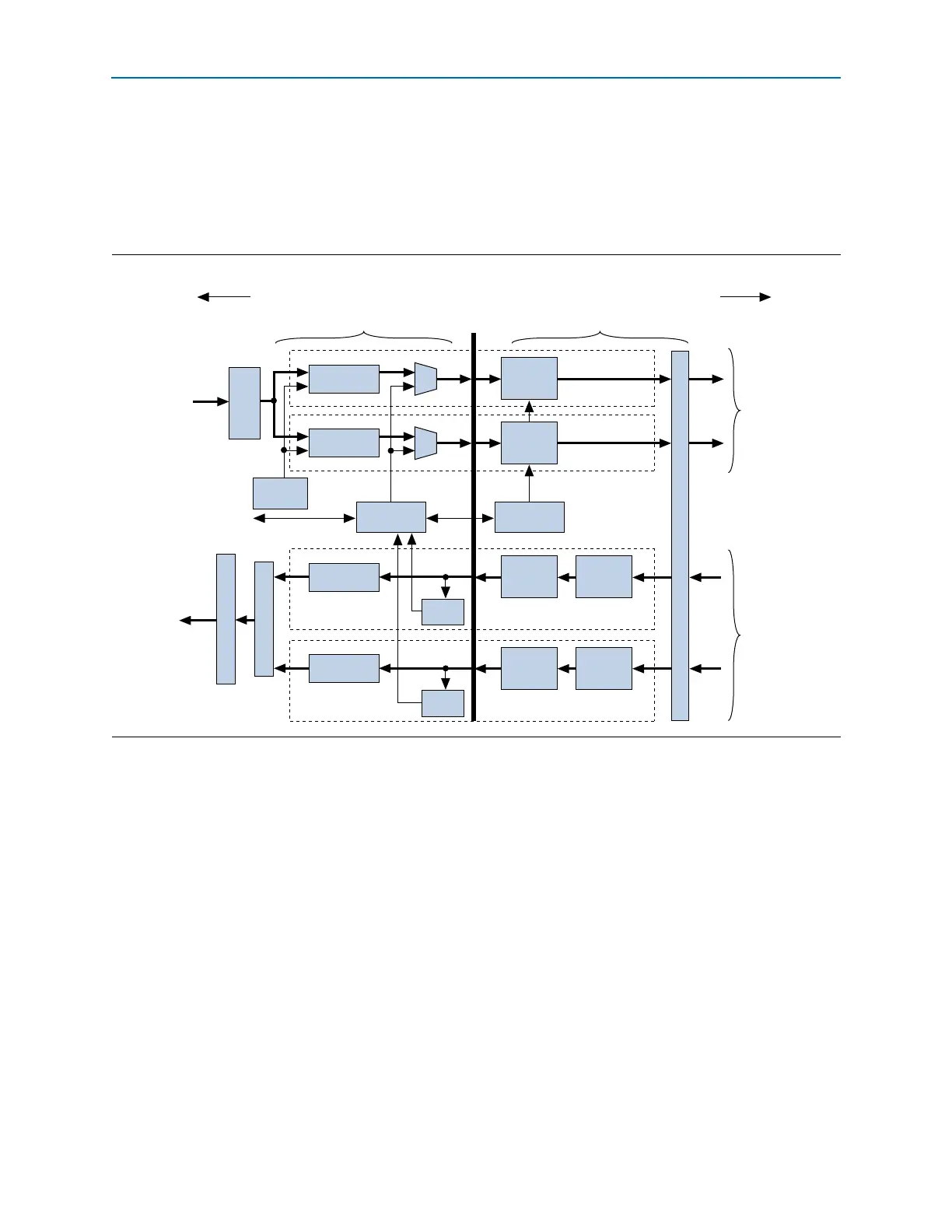

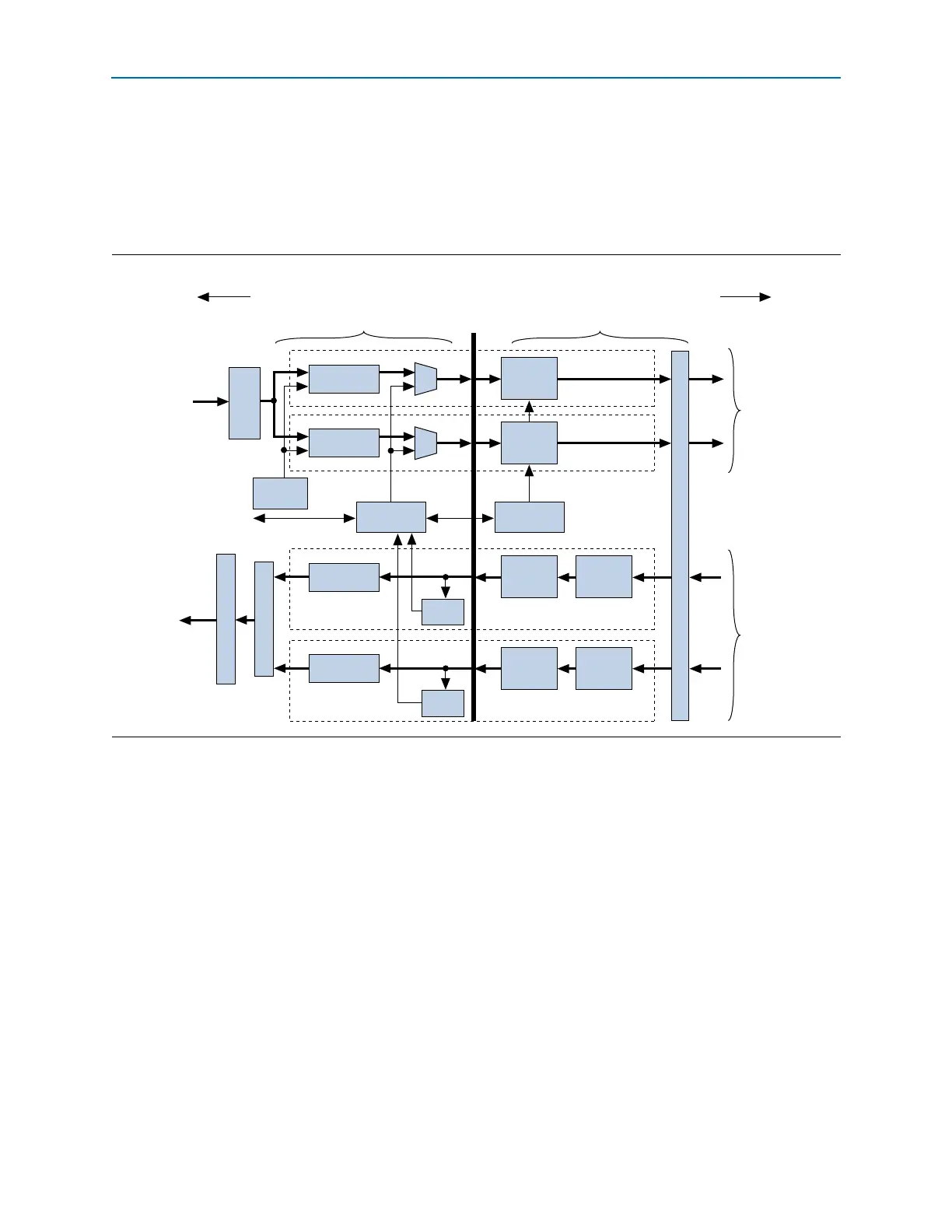

Figure 4–4 illustrates the Physical Layer architecture.

The Physical Layer is subdivided by the PIPE Interface Specification into two layers

(bracketed horizontally in Figure 4–4):

■ Media Access Controller (MAC) Layer—The MAC layer includes the LTSSM and

the scrambling/descrambling and multilane deskew functions.

■ PHY Layer—The PHY layer includes the 8B/10B encode/decode functions, elastic

buffering, and serialization/deserialization functions.

The Physical Layer integrates both digital and analog elements. Intel designed the

PIPE interface to separate the MAC from the PHY. The Cyclone V Hard IP for PCI

Express complies with the PIPE interface specification.

Figure 4–4. Physical Layer

Scrambler

8B10B

Encoder

Lane n

Tx+ / Tx-

Scrambler

8B10B

Encoder

Lane 0

Tx+ / Tx-

Descrambler

8B10B

Decoder

Lane n

Rx+ / Rx-

Elastic

Buffer

LTSSM

State Machine

SKIP

Generation

Control & Status

PIPE

Emulation Logic

Link Serial izer

Link Serial izer

Tx Packets

Rx MAC

Lane

Device Transceiver (per Lane) with 2.5 or 5.0 Gbps SERDES & PLL

Descrambler

8B10B

Decoder

Lane 0

Rx+ / Rx-

Elastic

Buffer

Rx MAC

Lane

PIPE

Interface

Multilane Deskew

Rx Packets

Transmit

Data Path

Receive

Data Path

MAC Layer PHY layer

To LinkTo Data Link Layer

Loading...

Loading...