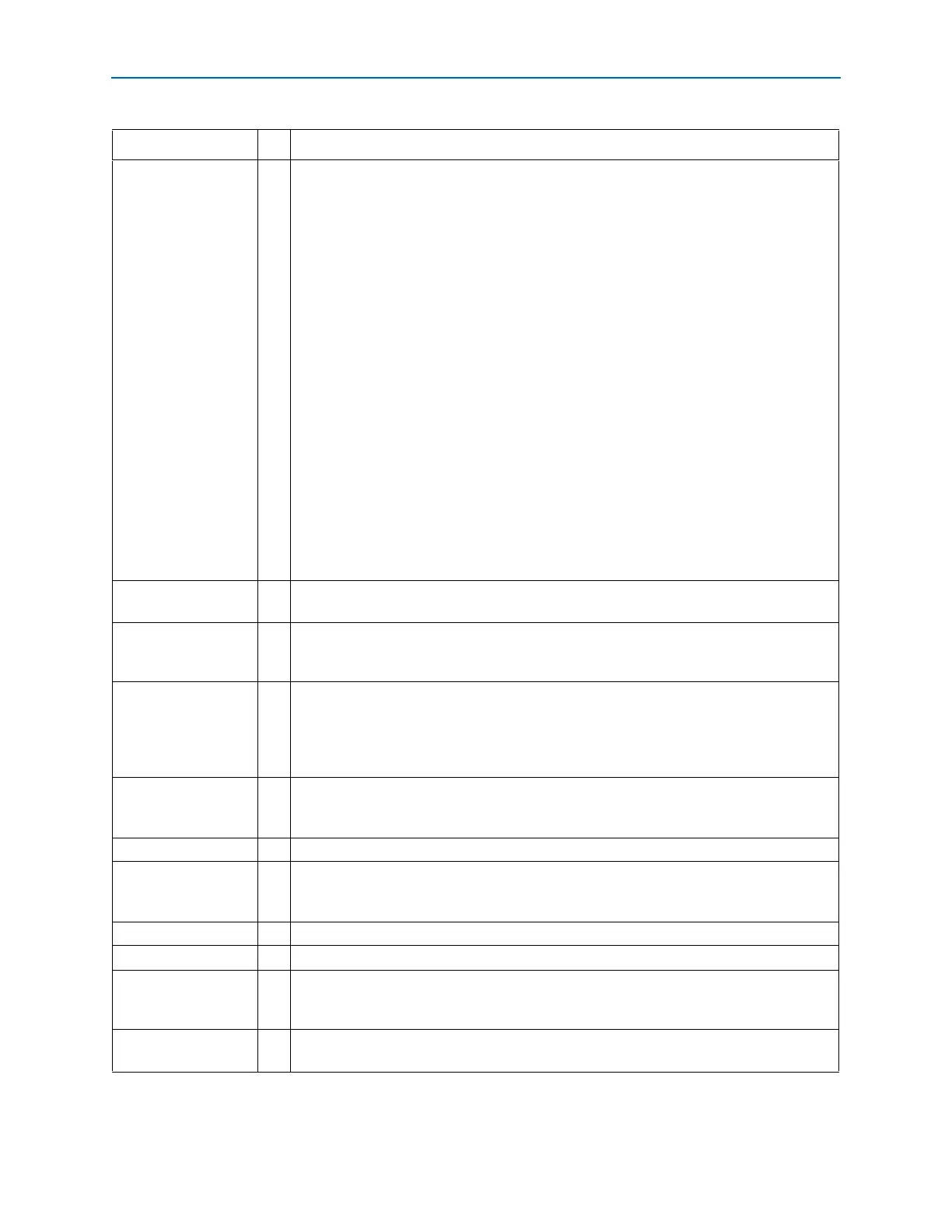

Chapter 5: IP Core Interfaces 5–15

Reset Signals

November 2011 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

pin_perstn

I

Active low reset from the PCIe reset pin of the device. This reset signal is an input to the

embedded reset controller for PCI Express in Cyclone V devices. It resets the datapath and

control registers. This signal is required for CvP. Cyclone V devices have 1 or 2 instances of

the Hard IP for PCI Express. Each instance has its own

pin_perst

signal.

Every Cyclone V devices has 2

nPERST

pins, even devices with fewer than 2 instances of the

Hard IP for PCI Express. These pins have the following locations:

■

nPERSTL0

: bottom left Hard IP and CvP blocks

■

nPERSTL1

: top left Hard IP block

For maximum use of the Cyclone V device, Altera recommends that you use the bottom left

Hard IP first. This is the only location that supports CvP over a PCIe link.

Refer to the appropriate Cyclone V device pinout for correct pin assignment for more

detailed information about these pins. The PCI Express Card Electromechanical Specification

2.0 specifies this pin to require 3.3 V. You can drive this 3.3V signal to the

pin_perst

pin

even if the V

CCIO

of the bank is not 3.3V if the following 2 conditions are met:

■ The input signal meets the V

IH

and V

IL

specification for LVTTL.

■

■

The input signal meets the overshoot specification for 100°C operation as specified by the

“Maximum Allowed Overshoot and Undershoot Voltage” section in the Device Datasheet

for Cyclone V Devices in volume 1 of the Cyclone Device Handbook.

Refer to Figure 5–14 on page 5–17 for a timing diagram illustrating the use of this signal.

serdes_pll_locked

O

When asserted, indicates that the PLL that generates the

coreclkout_hip

clock signal is

locked. In pipe simulation mode this signal is always asserted.

fixedclk_locked

O

When asserted, indicates that the PLL that provides the fixed clock required for transceiver

initialization is locked. The Application Layer should be held in reset until

fixedclk_locked

is asserted.

pld_core_ready

I

When asserted, indicates that the Application Layer is ready for operation and is providing a

stable clock to the

pld_clk

input. If the

coreclkout_hip

clock is the direct input to the

pld_clk

input, this input can be connected to the

serdes_pll_locked

output. If a

different clock drives

pld_clk

, the corresponding lock signal for that clock should be used

to drive this input.

pld_clk_inuse

O

When asserted, indicates that the Hard IP Transaction Layer is using the

pld_clk

as its

clock and is ready for operation with the Application Layer. For reliable operation, hold the

Application Layer in reset until

pld_clk_inuse

is asserted.

dlup

O When asserted, indicates that the Hard IP block is in the DLCSM DLUP state.

dlup_exit

O

This signal is active for one

pld_clk

cycle when the IP core exits the DLCSM DLUP state.

This signal should cause the Application Layer to assert a global reset. This signal is active

low and otherwise remains high.

ev128ns

O Asserted every 128 ns to create a time base aligned activity.

ev1us

O Asserted every 1 µs to create a time base aligned activity.

hotrst_exit

O

Hot reset exit. This signal is asserted for 1 clock cycle when the LTSSM exits the hot reset

state. This signal should cause the Application Layer to assert a global reset. This signal is

active low and otherwise remains high.

l2_exit

O

L2 exit. This signal is active low and otherwise remains high. It is asserted for one cycle

(changing value from 1 to 0 and back to 1) after the LTSSM transitions from l2_idl to detect.

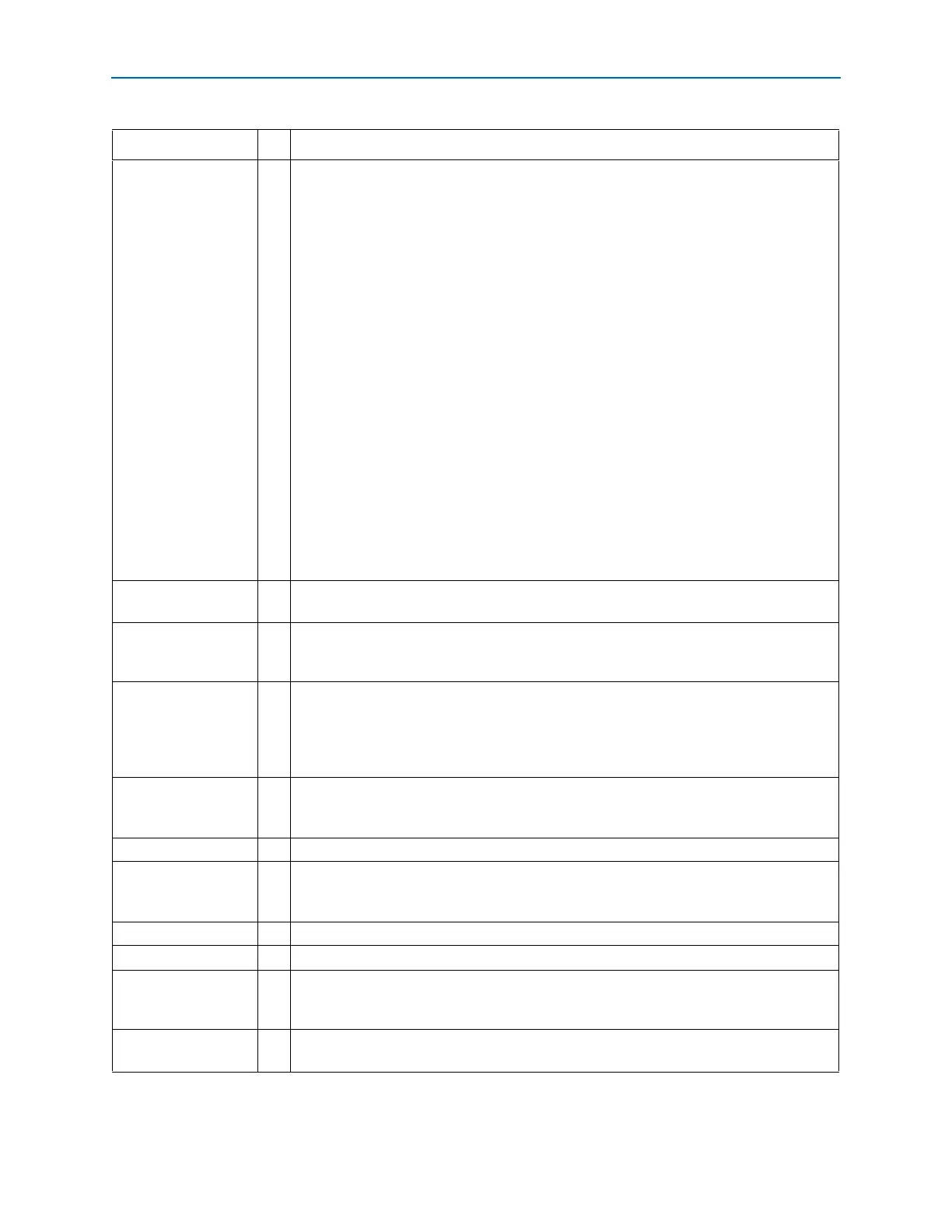

Table 5–6. Reset and Link Training Signals (Part 2 of 3)

Signal I/O Description

Loading...

Loading...