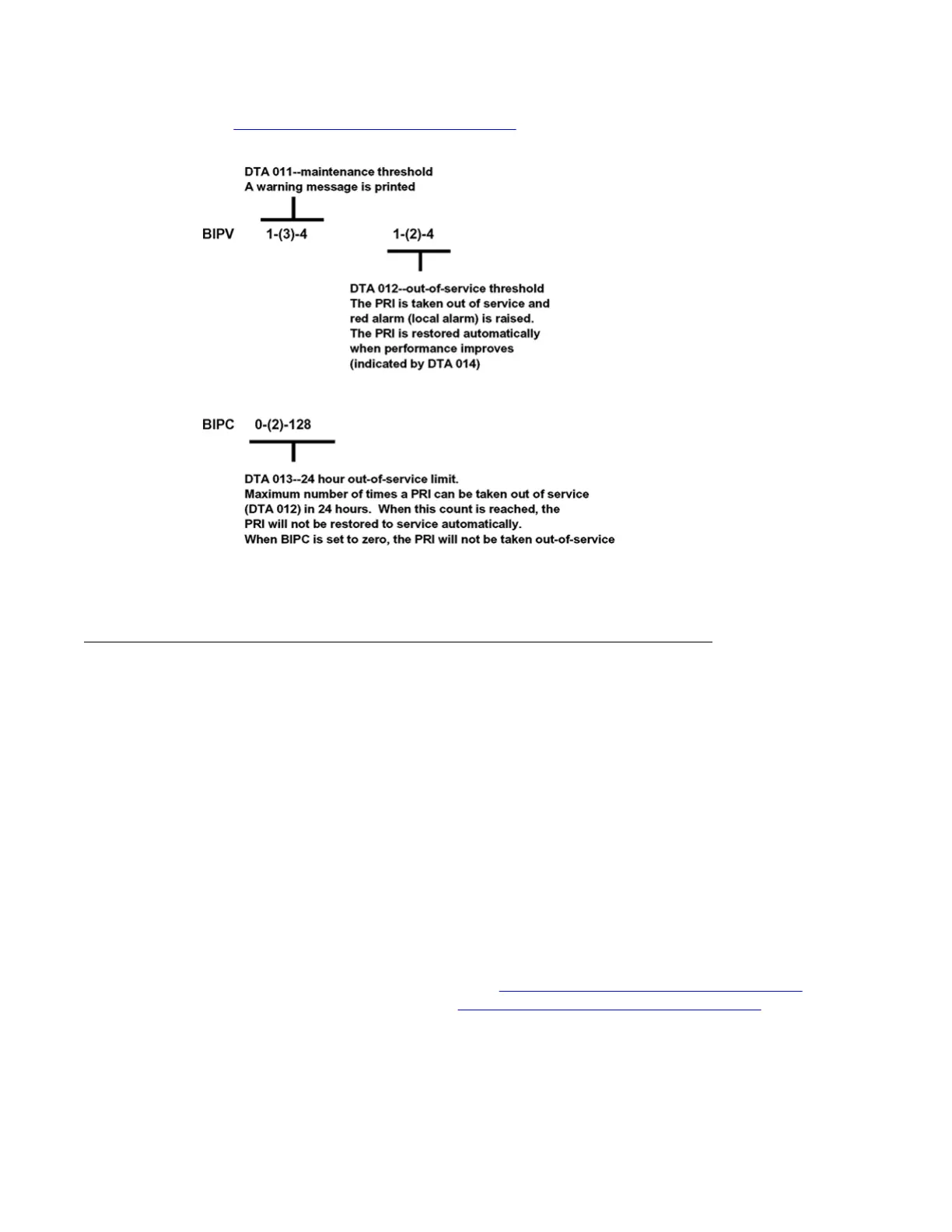

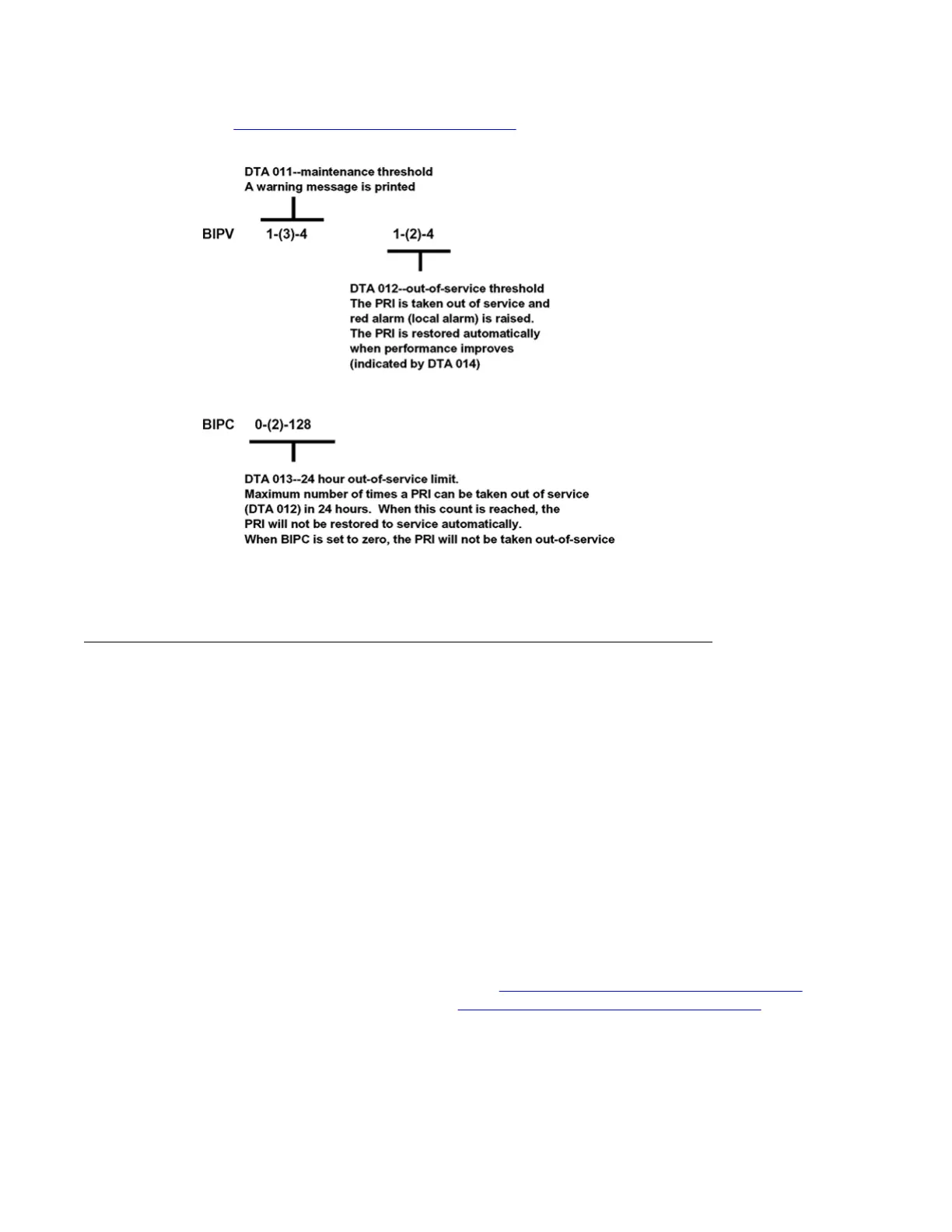

Refer to Figure 20: BIPV and BIPC thresholds on page 113 for BIPV and BIPC thresholds.

Figure 20: BIPV and BIPC thresholds

Frame slip

Digital signals must have accurate clock synchronization for data to be interleaved into, or

extracted from, the appropriate timeslot during multiplexing and de-multiplexing operations.

A

frame slip is defined as the repetition or deletion of the 193 data bits of a DS-1 frame due to a

sufficiently large discrepancy in the read and write rates at the buffer (clocks aren't operating

at exactly the same speed).

When data bits are written into (added to) a buffer at a slightly higher rate than that at which

they are being read (emptied), sooner or later the buffer overflows. This is a slip-frame

deletion.

In the opposite situation, when data bits are written (added) into a buffer at slightly lower rate

than that at which they are read (emptied), eventually the buffer runs dry or underflows. This

is also a slip-frame repetition.

Either occurrence is called a slip (or a controlled slip). The system contains a buffer large

enough to hold about 2 full DS-1 frames (193 * 2 = 386). It is normally kept half-full (1 frame).

Slippage impacts data transfer as shown in

Table 50: Impact of slip on service types on

page 1

14. The degradations shown in

Table 50: Impact of slip on service types on page 1

14

can be controlled or avoided with proper clock (network) synchronization.

DTI/PRI maintenance tools

ISDN Primary Rate Interface Maintenance November 2011 113

Loading...

Loading...